- 摘要:基于FPGA和USB2.0的技術方案,設計了一種高速化和集成化的數據采集系統。該系統是以Altera公司的FPGA芯片EP2C5T144為主控芯片,以Cypress公司的EZ-USB FX2芯片為傳輸手段設計實現的。首先詳細介紹了整體系統的

- 關鍵字:

FPGA 數據采集系統

- 摘要:激光雷達的發射波及回波信號經光電器件轉換形成的電信號具有脈寬窄,幅度低,背景噪聲大等特點,對其進行低速數據采集存在數據精度不高等問題。同時,A/D轉換器與數字信號處理器直接連接會導致數據傳輸不

- 關鍵字:

FPGA DSP 雷達 高速數據

- 摘要:為了提高系統的集成度和可靠性,降低功耗和成本,增強系統的靈活性,提出一種采用非常高速積體電路的硬件描述語言(VHDL語言)來設計數字基帶傳輸系統的方法。詳細闡述數字基帶傳輸系統中信號碼型的設計原則,數

- 關鍵字:

FPGA 數字基帶 傳輸系統

- 市場分析師預測,全球營收排名第二大的可程序化邏輯組件供貨商Altera,有機會在2012年初取代該市場龍頭Xilinx躍上第一大供貨商位置。

- 關鍵字:

Altera FPGA

- 為達到IRIG-B碼與時間信號輸入、輸出的精確同步,采用現代化靶場的IRIG-B碼編碼和解碼的原理,從工程的角度出發,提出了使用現場可編程門陣列(FPGA)來實現IRIG-B碼編碼和解碼的設計方案和體系結構,設計中會涉及到幾個不同的時鐘頻率,FPGA對時鐘的同步性具有靈活性、效率高、且功耗低。抗干擾性好的特點。結果表明,FPGA能夠確保為從設備提供同源的時鐘基準,使時鐘與信號的延遲控制在200 ns以內,從而得到了IRIG-B碼與時間精確同步的效果。

- 關鍵字:

IRIG-B FPGA DC 編碼

- 激光雷達的發射波及回波信號經光電器件轉換形成的電信號具有脈寬窄,幅度低,背景噪聲大等特點,對其進行低速數據采集存在數據精度不高等問題。同時,A/D轉換器與數字信號處理器直接連接會導致數據傳輸不及時,影響系統可靠性、實時性。針對激光雷達回撥信號,提出基于FPGA與DSP的高速數據采集系統,利用FPGA內部的異步FIFO和DCM實現A/D轉換器與DSP的高速外部存儲接口(EMIF)之間的數據傳輸。介紹了ADC外圍電路、工作時序以及DSP的EMIF的設置參數,并對異步FIFO數據讀寫進行仿真,結合硬件結構詳細地

- 關鍵字:

FPGA DSP 雷達 高速數據

- 為進行高精度信號源的設計,同時降低設計成本,以Cyclone II系列低端FPGA為核心,利用直接頻率合成技術,對正弦信號等數據進行1/4周期壓縮存儲到ROM中,在外部時鐘頻率為50 MHz,實現了正弦信號源的設計,同時,實現三角波、鋸齒波、矩形脈沖及2-ASK、2-PSK和2-FSK等數字調制信號,系統還具有掃頻、指定波形次數等功能。仿真結果表明,信號源精度高,頻率調整步進可達0.034 92 Hz,頻率范圍為0.034 92 Hz~9.375 MHz,制作成本低,功能豐富。

- 關鍵字:

DDFS FPGA 高精度 信號源

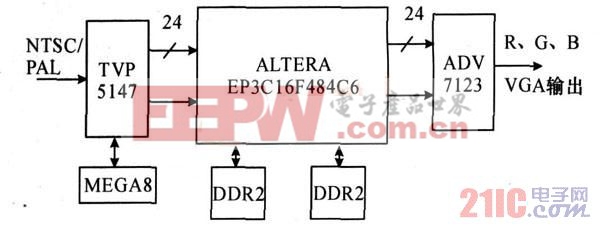

- 摘 要: 針對電視制式PAL /NTSC 信號輸出VGA 顯示格式的解決辦法,詳細講述了基于FPGA 視頻格式轉換系統的設計實現。采用Cyclone Ⅲ系列的EP3C1*84C6作為核心處理器件,實現了NTSC /PAL制式視頻的解碼、色空間轉換(

- 關鍵字:

系統 設計 轉換 格式 FPGA 視頻 基于

- 摘 要:文章中提出了一種應用于FPGA 的嵌入式可配置雙端口的塊存儲器。該存儲器包括與其他電路的布線接口、可配置邏輯、可配置譯碼、高速讀寫電路。在編程狀態下,可對所有存儲單元進行清零,且編程后為兩端口獨

- 關鍵字:

FPGA SRAM 嵌入式

- 1 設計要求 設計并制作一個數字化語音存儲與回放系統,其示意圖如圖1所示。

圖1 數字化語音存儲與回放系統示意圖 (1)放大器1的增益為46dB,放大器2的增益為40dB,增益均可調; (2)帶通濾波器:通帶為30

- 關鍵字:

FPGA 語音存儲 回放 系統設計

- 摘 要:為了取代傳統利用單片機驅動微型打印機,使用Alt era 公司的FPGA 芯片EP3C25Q240C8N 設計驅動打印機的硬件控制電路,并正確控制微型打印機的工作時序。軟件使用硬件描述語言VH DL 實現對微型打印機的時序控

- 關鍵字:

FPGA VHDL 微型打印機 驅動設計

- 在便攜式數字衛星通信系統中,為了擴大傳輸容量和提高傳輸效率,滿足同時傳輸幾種業務的需求,通常采用時分復用的方法,將若干個低速數字碼流按一定格式合并成一個高速數據碼流,以便在一條信道中傳輸,使各個業務信

- 關鍵字:

FPGA 衛星 便攜 數字復接器

- 摘要:提出了基于電路分割技術實現通信系統發送端根升余弦波形成形濾波器查表法的FPGA結構,節省了ROM單元,討論了其ROM初始化時形波數據的組織方法,完成了該結構的VHDL實現,給出了該設計在Modelsim環境下的時序仿

- 關鍵字:

FPGA 脈沖 成形濾波器

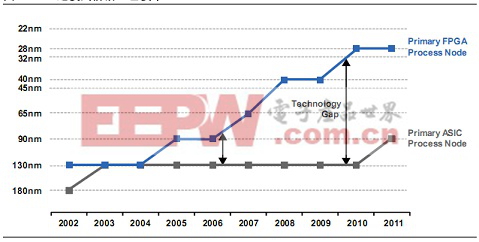

- SoC FPGA上的策略考慮,引言 集成了 FPGA 架構、硬核 CPU 子系統以及其他硬核 IP 的半導體器件 SoC FPGA 已經發展到了一個“關鍵點”,它在今后十年中會得到廣泛應用,為系統設計人員提供更多的選擇。對于在 FPGA 上開發的系統

- 關鍵字:

考慮 策略 FPGA SoC

- PLD/FPGA硬件語言設計verilog HDL,HDL概述 隨著EDA技術的發展,使用硬件語言設計PLD/FPGA成為一種趨勢。目前最主要的硬件描述語言是VHDL和verilog HDL及System Verilog。 VHDL發展的較早,語法嚴格;而Verilog HDL是在C語言的基礎上發展起來的一種硬

- 關鍵字:

verilog HDL 設計 語言 硬件 PLD/FPGA

rf-fpga介紹

您好,目前還沒有人創建詞條rf-fpga!

歡迎您創建該詞條,闡述對rf-fpga的理解,并與今后在此搜索rf-fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473