EEPW首頁(yè) >>

主題列表 >>

risc-v ip

risc-v ip 文章 最新資訊

CEVA將在上海世界移動(dòng)通信大會(huì)展示消費(fèi)類(lèi)電子用芯片和軟件IP

- 全球領(lǐng)先的無(wú)線連接和智能感知技術(shù)及共創(chuàng)解決方案的授權(quán)許可廠商CEVA, Inc.(納斯達(dá)克股票代碼:CEVA)參加2023年6月28至30日在上海舉辦的世界移動(dòng)通信大會(huì)。在這次展會(huì)上,CEVA團(tuán)隊(duì)將與SoC和OEM客戶(hù)面對(duì)面溝通交流,探討最新的技術(shù)創(chuàng)新,并介紹如何充分利用CEVA IP開(kāi)發(fā)無(wú)線連接和智能感知應(yīng)用以實(shí)現(xiàn)產(chǎn)品設(shè)計(jì)目標(biāo)。 CEVA將在行政會(huì)議室展示用于邊緣AI、5G、計(jì)算機(jī)視覺(jué)、空間音頻(spatial-audio)和物聯(lián)網(wǎng)連接的最新解決方案,包括: ● 邊緣AI推

- 關(guān)鍵字: CEVA 上海世界移動(dòng)通信大會(huì) IP

利用先進(jìn)形式驗(yàn)證工具來(lái)高效完成RISC-V處理器驗(yàn)證

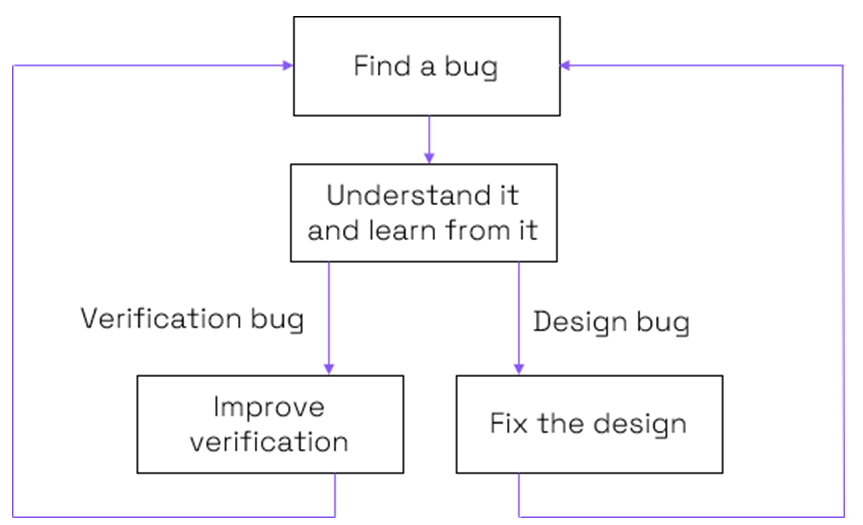

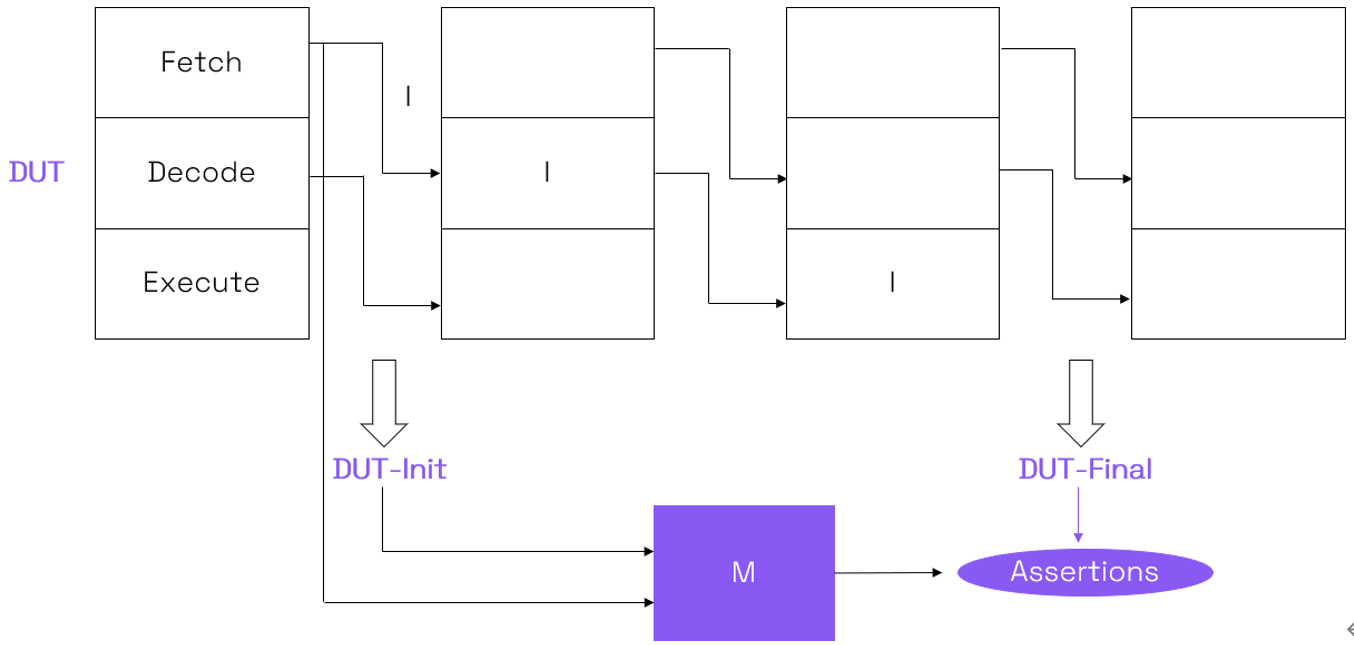

- 我們?cè)谏弦黄夹g(shù)白皮書(shū)《基于形式驗(yàn)證的高效RISC-V處理器驗(yàn)證方法》中,以Codasip L31這款用于微控制器應(yīng)用的32位中端嵌入式RISC-V處理器內(nèi)核為例,介紹了一個(gè)基于形式驗(yàn)證的、易于調(diào)動(dòng)的RISC-V處理器驗(yàn)證程序。它與RISC-V ISA黃金模型和RISC-V合規(guī)性自動(dòng)生成的檢查一起,展示了如何有效地定位那些無(wú)法進(jìn)行仿真的漏洞。RISC-V的開(kāi)放性允許定制和擴(kuò)展基于RISC-V內(nèi)核的架構(gòu)和微架構(gòu),以滿(mǎn)足特定需求。這種對(duì)設(shè)計(jì)自由的渴望也正在將驗(yàn)證部分的職責(zé)轉(zhuǎn)移到不斷壯大的開(kāi)發(fā)人員社群。然而,隨

- 關(guān)鍵字: 形式驗(yàn)證工具 RISC-V 驗(yàn)證

IAR與先楫半導(dǎo)體達(dá)成戰(zhàn)略合作,支持先楫RISC-V MCU開(kāi)發(fā)

- (中國(guó)|上海)2023年6月14日 - 在Embedded World China首屆展會(huì)舉辦期間,嵌入式開(kāi)發(fā)軟件和服務(wù)的全球領(lǐng)導(dǎo)者 IAR 與國(guó)產(chǎn)領(lǐng)先高性能MCU廠商先楫半導(dǎo)體(HPMicro)共同宣布達(dá)成戰(zhàn)略合作協(xié)議:IAR 最新的 Embedded Workbench for RISC-V 版本將全面支持先楫HPM6000高性能RISC-V MCU系列,這是IAR 首次支持高性能通用RISC-V MCU產(chǎn)品系列。IAR為先楫半導(dǎo)體的創(chuàng)新產(chǎn)品提供全面的開(kāi)發(fā)工具支持,包括

- 關(guān)鍵字: IAR 先楫 RISC-V MCU

2023 SiFive RISC-V中國(guó)技術(shù)論壇即將盛大開(kāi)幕

- 指令精簡(jiǎn)、模塊化、可擴(kuò)展……已于2022年利用7年時(shí)間達(dá)成出貨量100億顆的里程碑,RSIC-V正在充分發(fā)揮自身的開(kāi)放開(kāi)源優(yōu)勢(shì),一路開(kāi)疆拓土。身為RISC-V的發(fā)明者與領(lǐng)導(dǎo)廠商,SiFive正發(fā)揮開(kāi)源生態(tài)疊加未來(lái)計(jì)算新范式的“鏈主”效應(yīng),致力于將RISC-V的無(wú)限潛力引領(lǐng)至高性能處理器與高算力場(chǎng)景應(yīng)用中。?同時(shí),100億顆RISC-V處理器芯片中,近一半產(chǎn)自中國(guó)的亮眼數(shù)據(jù)有目共睹,RISC-V在中國(guó)市場(chǎng)信心持續(xù)走高,在此大環(huán)境背景下,SiFive親自運(yùn)營(yíng)中國(guó)市場(chǎng)與業(yè)務(wù),希望和中國(guó)一起見(jiàn)證RISC

- 關(guān)鍵字: SiFive RISC-V

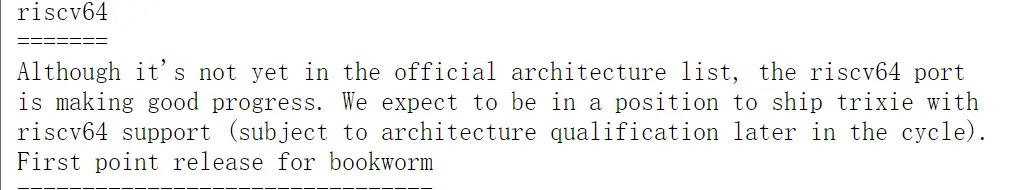

Debian 13“Trixie”Linux 發(fā)行版有望將帶來(lái) RISC-V 64 位支持

- IT之家 6 月 12 日消息,Debian 是最為古老的 GNU / Linux 發(fā)行版之一,該操作系統(tǒng)以穩(wěn)定性為重,不追求高速迭代,因此在新版本發(fā)布很早以前,就會(huì)揭曉一系列新特性。目前 Debian 項(xiàng)目宣布,在未來(lái)的 Debian 13 “Trixie” 中,將帶來(lái) RISC-V 64 位支持。日前 Debian 發(fā)布團(tuán)隊(duì)分享的更新郵件中,Debian 開(kāi)發(fā)人員 Jonathan Wiltshire 透露了 RISC-V 架構(gòu)下 Debian 的現(xiàn)狀:“雖然 RISC-V 64 位移植在此

- 關(guān)鍵字: RISC-V

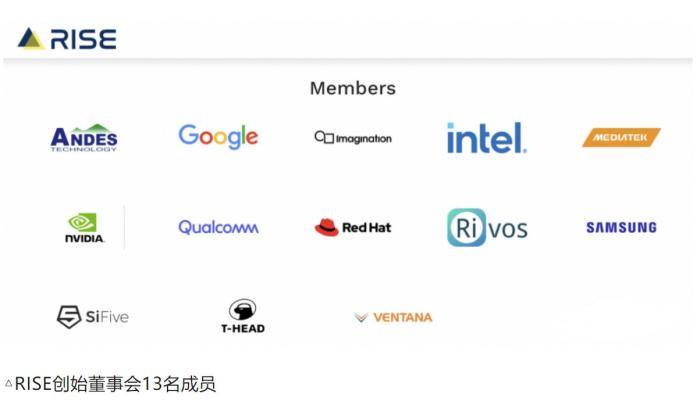

三星、英特爾、高通等 13 家企業(yè)發(fā)起 RISC-V 軟件生態(tài)計(jì)劃 RISE

- IT之家 6 月 2 日消息,三星、英特爾、英偉達(dá)、高通、聯(lián)發(fā)科、谷歌等 13 家 IT 和半導(dǎo)體企業(yè)今日在比利時(shí)布魯塞爾正式發(fā)起全球 RISC-V 軟件生態(tài)計(jì)劃“RISE”。據(jù)介紹,該計(jì)劃旨在加速 RISC-V 新架構(gòu)的軟件生態(tài)建設(shè)及應(yīng)用商業(yè)化進(jìn)程,推動(dòng) RISC-V 處理器在移動(dòng)通信、數(shù)據(jù)中心、邊緣計(jì)算及自動(dòng)駕駛等領(lǐng)域的市場(chǎng)化落地。RISE 創(chuàng)始董事會(huì)包含 13 名成員:谷歌、英特爾、平頭哥、三星、聯(lián)發(fā)科、英偉達(dá)、高通、Andes、Imagination、Red Hat、Rivos、SiFive、Ve

- 關(guān)鍵字: RISC-V

RISC-V切入云計(jì)算的元年,進(jìn)展如何了?

- 近兩年,RISC-V 作為 IT 產(chǎn)業(yè)鏈中國(guó)產(chǎn)替代中的重要一環(huán)備受關(guān)注。這個(gè)基于 BSD 協(xié)議開(kāi)源,基金會(huì)總部設(shè)在瑞士的開(kāi)源指令集也一直被視為 X86 和 ARM 強(qiáng)有力的競(jìng)爭(zhēng)對(duì)手。不過(guò),由于起步較晚,性能與生態(tài)尚未成熟,RISC-V 以往更多地是用在物聯(lián)網(wǎng)領(lǐng)域。今年,算能科技基于阿里平頭哥玄鐵 C910 開(kāi)發(fā)了一臺(tái) 64 核 RISC-V 服務(wù)器 SG2042。這一動(dòng)作則拉開(kāi)了 RISC-V 挺入云計(jì)算領(lǐng)域的序幕,2023 也被業(yè)界看做是 RISC-V 進(jìn)入云計(jì)算的元年。本期開(kāi)源訪談我們邀請(qǐng)中國(guó)電信研究

- 關(guān)鍵字: RISC-V 崔恩放

阿里加入RISC-V官方組織,還有高通、三星、intel也加入了

- 在ARM、X86芯片架構(gòu)之后,最被大家看好的芯片架構(gòu)就是RISC-V了。特別是中國(guó)芯片廠商,紛紛擁抱RISC-V架構(gòu),原因在于RISC-V架構(gòu)是開(kāi)源免費(fèi)的,不怕被人卡脖子。所以我們看到中科院、阿里紛紛推出了眾多的RISC-V芯片,2022年全球出貨100億顆RISC-V芯片中,50%是中國(guó)廠商貢獻(xiàn)的。也正因?yàn)镽ISC-V架構(gòu)的火爆,最近全球13家知名IT巨頭,成立了一個(gè)RISC-V軟件生態(tài)系統(tǒng) (RISE) 的指導(dǎo)委員會(huì)。這個(gè)委員會(huì)的目的,就是推進(jìn)RISC-V芯片的落地,加速RISC-V新架構(gòu)的軟件生態(tài)建

- 關(guān)鍵字: RISC-V 阿里

科技巨頭聯(lián)合發(fā)起RISC-V生態(tài)計(jì)劃 年出貨將超800億顆

- 據(jù)報(bào)道,由谷歌、英特爾、平頭哥等13家企業(yè)發(fā)起的全球RISC-V軟件生態(tài)計(jì)劃“RISE”,在比利時(shí)布魯塞爾正式啟動(dòng)。RISE旨在加速RISC-V新架構(gòu)的軟件生態(tài)建設(shè)及應(yīng)用商業(yè)化進(jìn)程,成員將聯(lián)合推動(dòng)RISC-V處理器在移動(dòng)通信、數(shù)據(jù)中心、邊緣計(jì)算及自動(dòng)駕駛等領(lǐng)域的市場(chǎng)化落地。面對(duì)物聯(lián)網(wǎng)等應(yīng)用新變化,RISC-V作為新一代指令集,擁有開(kāi)源、精簡(jiǎn)、靈活、可自定義的特點(diǎn),相比封閉的ARM指令集,更適合專(zhuān)用處理器的開(kāi)發(fā),有望在IoT MCU市場(chǎng)迅速擴(kuò)張,而后推廣至數(shù)據(jù)中心等領(lǐng)域。我國(guó)RISC-V發(fā)展意義更加重大,在

- 關(guān)鍵字: RISC-V

基于形式驗(yàn)證的高效RISC-V處理器驗(yàn)證方法

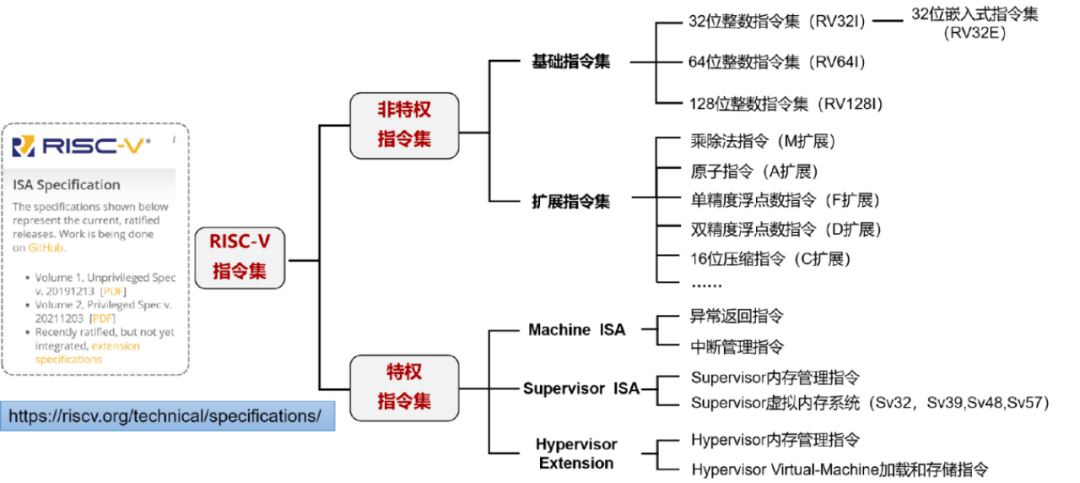

- RISC-V的開(kāi)放性允許定制和擴(kuò)展基于 RISC-V 內(nèi)核的架構(gòu)和微架構(gòu),以滿(mǎn)足特定需求。這種對(duì)設(shè)計(jì)自由的渴望也正在將驗(yàn)證部分的職責(zé)轉(zhuǎn)移到不斷壯大的開(kāi)發(fā)人員社群。然而,隨著越來(lái)越多的企業(yè)和開(kāi)發(fā)人員轉(zhuǎn)型RISC-V,大家才發(fā)現(xiàn)處理器驗(yàn)證絕非易事。新標(biāo)準(zhǔn)由于其新穎和靈活性而帶來(lái)的新功能會(huì)在無(wú)意中產(chǎn)生規(guī)范和設(shè)計(jì)漏洞,因此處理器驗(yàn)證是處理器開(kāi)發(fā)過(guò)程中一項(xiàng)非常重要的環(huán)節(jié)。在復(fù)雜性一般的RISC-V 處理器內(nèi)核的開(kāi)發(fā)過(guò)程中,會(huì)發(fā)現(xiàn)數(shù)百甚至數(shù)千個(gè)漏洞。當(dāng)引入更多高級(jí)特性的時(shí)候,也會(huì)引入復(fù)雜程度各不相同的新漏洞。而某些類(lèi)

- 關(guān)鍵字: 形式驗(yàn)證 RISC-V

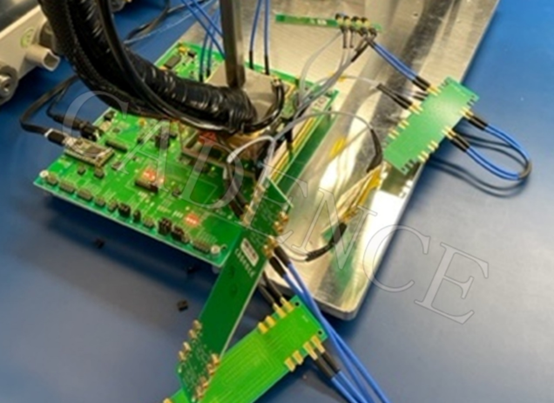

Cadence發(fā)布面向TSMC 3nm工藝的112G-ELR SerDes IP展示

- 3nm 時(shí)代來(lái)臨了!Cadence 在 2023 年 TSMC 北美技術(shù)研討會(huì)期間發(fā)布了面向臺(tái)積電 3nm 工藝(N3E)的 112G 超長(zhǎng)距離(112G-ELR)SerDes IP 展示,這是 Cadence 112G-ELR SerDes IP 系列產(chǎn)品的新成員。在后摩爾時(shí)代的趨勢(shì)下,F(xiàn)inFET 晶體管的體積在 TSMC 3nm 工藝下進(jìn)一步縮小,進(jìn)一步采用系統(tǒng)級(jí)封裝設(shè)計(jì)(SiP)。通過(guò)結(jié)合工藝技術(shù)的優(yōu)勢(shì)與 Cadence 業(yè)界領(lǐng)先的數(shù)字信號(hào)處理(DSP)SerDes 架構(gòu),全新的 112G-ELR

- 關(guān)鍵字: Cadence TSMC 3nm工藝 SerDes IP

歐洲RISC-V處理器流片:216核心 不需要風(fēng)扇散熱

- 5月9日消息,歐洲航天局(ESA)贊助、瑞士蘇黎世聯(lián)邦理工學(xué)院和意大利博洛尼亞大學(xué)共同開(kāi)發(fā)的“Occany”(鳥(niǎo)蛇)處理器,現(xiàn)已流片。這顆處理器基于開(kāi)源開(kāi)放的RISC-V架構(gòu),GlobalFoundries 12nm LPP低功耗工藝,chiplet小芯片設(shè)計(jì),2.5D封裝,雙芯片共集成多達(dá)216個(gè)核心,晶體管數(shù)量達(dá)10億個(gè),而面積僅為73平方毫米。同時(shí),它還集成了未公開(kāi)數(shù)量的64位FPU浮點(diǎn)單元,整合兩顆美光的16GB HBM2e高帶寬內(nèi)存。硅中介層面積26.3 x 23.05毫米,制造工藝為65nm,

- 關(guān)鍵字: risc-v 架構(gòu) 處理器

芯原股份:公司的神經(jīng)網(wǎng)絡(luò)處理器IP系列產(chǎn)品可廣泛適用于AIoT、智慧汽車(chē)等應(yīng)用場(chǎng)景

- 2023年5月8日,芯原股份(688521.SH)在互動(dòng)平臺(tái)表示,芯原用于人工智能的神經(jīng)網(wǎng)絡(luò)處理器IP(NPU)業(yè)界領(lǐng)先,已經(jīng)在10多個(gè)領(lǐng)域、60多家客戶(hù)的110多款芯片中被采用。根據(jù)目前市場(chǎng)的需求,芯原基于自身神經(jīng)網(wǎng)絡(luò)處理器IP可伸縮可擴(kuò)展的特性,已發(fā)展了覆蓋從高性能云計(jì)算到低功耗邊緣計(jì)算的垂直解決方案;同時(shí)還推出了從攝像頭輸入到顯示器輸出的完整智能像素解決方案。因此,在人工智能領(lǐng)域,芯原的神經(jīng)網(wǎng)絡(luò)處理器IP系列產(chǎn)品可廣泛適用于包括智慧物聯(lián)網(wǎng)(AIoT)、智慧汽車(chē)、智慧可穿戴、智慧家居、視頻數(shù)據(jù)中心、智

- 關(guān)鍵字: 芯原股份 IP 神經(jīng)網(wǎng)絡(luò)處理器IP

楷登電子成功流片基于臺(tái)積電N3E工藝的16G UCIe先進(jìn)封裝IP

- 近日,楷登電子(Cadence)宣布基于臺(tái)積電3nm(N3E)工藝技術(shù)的Cadence? 16G UCIe? 2.5D先進(jìn)封裝IP成功流片。該IP采用臺(tái)積電3D Fabric? CoWoS-S硅中介層技術(shù)實(shí)現(xiàn),可提供超高的帶寬密度、高效的低功耗性能和卓越的低延遲,非常適合需要極高算力的應(yīng)用。據(jù)悉,楷登電子目前正與許多客戶(hù)合作,來(lái)自N3E測(cè)試芯片流片的UCIe先進(jìn)封裝IP已開(kāi)始發(fā)貨并可供使用。這個(gè)預(yù)先驗(yàn)證的解決方案可以實(shí)現(xiàn)快速集成,為客戶(hù)節(jié)省時(shí)間和精力。

- 關(guān)鍵字: 楷登電子 臺(tái)積電 N3E UCIe 先進(jìn)封裝 IP

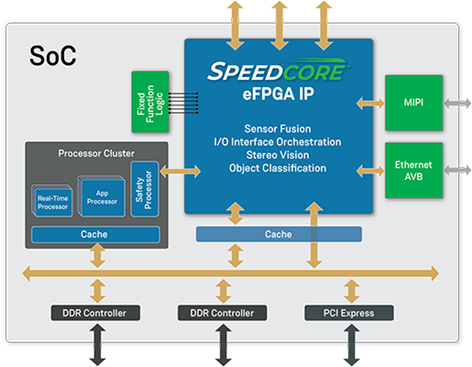

為什么嵌入式FPGA(eFPGA)IP是ADAS應(yīng)用的理想選擇?

- 提高汽車(chē)電氣化和自動(dòng)駕駛的一個(gè)主要方面是先進(jìn)駕駛輔助系統(tǒng)(ADAS)的普及。如今,這些系統(tǒng)正迅速應(yīng)用于市場(chǎng)上幾乎所有的車(chē)輛,而且隨著技術(shù)的成熟,這一趨勢(shì)只會(huì)持續(xù)下去。然而,隨著技術(shù)的發(fā)展,ADAS設(shè)計(jì)人員面臨的硬件挑戰(zhàn)變得越來(lái)越復(fù)雜。在本文中,我們將介紹ADAS的硬件需求,F(xiàn)PGA如何填補(bǔ)這些空白,以及為什么eFPGA IP將成為下一個(gè)ADAS硬件趨勢(shì)。ADAS的硬件要求ADAS在現(xiàn)代汽車(chē)中的發(fā)展給底層硬件帶來(lái)了一些嚴(yán)峻的挑戰(zhàn)。在像ADAS這樣的關(guān)鍵任務(wù)應(yīng)用中,最重要的目標(biāo)是確保車(chē)輛乘員的安全。這個(gè)目標(biāo)要

- 關(guān)鍵字: 嵌入式FPGA eFPGA IP ADAS

risc-v ip介紹

您好,目前還沒(méi)有人創(chuàng)建詞條risc-v ip!

歡迎您創(chuàng)建該詞條,闡述對(duì)risc-v ip的理解,并與今后在此搜索risc-v ip的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)risc-v ip的理解,并與今后在此搜索risc-v ip的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢(xún)有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢(xún)有限公司