- 世界領先的先進半導體解決方案供應商三星電子與ARM公司近日在于巴塞羅那舉行的世界移動通信大會上共同宣布:三星電子已經采用ARM Mali圖形處理器架構,用于未來具有圖形處理功能的片上系統(SoC)IC芯片以及其ASIC和代工業務。該協議標志著雙方在圖形技術上的長期戰略合作。

三星電子擁有為眾多市場開發基于ARM技術的尖端、復雜的片上系統的豐富經驗,這些市場包括手機、家庭娛樂和導航應用。Mali圖形技術滿足了從汽車電子到家庭娛樂等眾多領域中的產品對先進的互動圖形處理的需求。

三星電子系統大規

- 關鍵字:

三星電子 SoC ASIC ARM

- 一、摘要 從簡單SRAM接口到高速同步接口,TimingDesigner軟件允許設計者在設計流程的初期就判斷出潛在的時序問題,盡最大可能在第一時間解決時序問題。在設計過程的早期檢測到時序問題,不僅節省時間,而且可以更

- 關鍵字:

FPGA 時序

- 1 引言 20世紀末,全球范圍內興起的信息革命浪潮,為汽車工業的突破性發展提供了千載難逢的機遇,信息技術的廣泛應用是解決汽車帶來的諸如交通擁擠、交通安全、環境污染、能源枯竭等問題的最佳途徑。同時,隨著

- 關鍵字:

FPGA DSP 汽車電子

- 本白皮書介紹FPGA中的壓穩態,為什么會出現這一現象,它是怎樣導致設計失敗的。介紹怎樣計算壓穩態MTBF,重...

- 關鍵字:

FPGA 壓穩態 MTBF 寄存器

- MicroTCA正在成為嵌入信號處理應用,尤其是高性能的多處理器系統中日益普及的標準。這些標準采用了可滿足“運營商級”電信設備需求的先進中間卡(AdvancedMC),從而找到了進入電信應用的途徑,如無線基帶處理。

- 關鍵字:

FPGA RapidIO 無線 導入 MicroTCA

- 深圳芯海科技公司近日宣布推出低功耗SoC衡器計量芯片CSU11xx系列,包括CSU1182、CSU1181、及CSU1100三款產品。可降低電子衡器、精密測量及控制系統的待機與工作功耗,并降低整體實現成本。例如,對于太陽能電子秤的開發,既保證人體秤測量精度,同時工作電流小于20μA。

CSU1182、CSU1181、及CSU1100集成了8位RISCMCU,2K/4K*16OTP(可作為用戶數據PROM)、128/256RAM、4*14/18LCD,以及16個I/O口(此外,所有的&ldq

- 關鍵字:

芯海科技 SoC CSU1182 CSU1181 及CSU1100

- 基于FPGA的高速定點FFT算法的設計方案,引 言

快速傅里葉變換(FFT)作為計算和分析工具,在眾多學科領域(如信號處理、圖像處理、生物信息學、計算物理、應用數學等)有著廣泛的應用。在高速數字信號處理領域,如雷達信號處理,FFT的處理速度往往是整個系

- 關鍵字:

算法 設計 方案 FFT 定點 FPGA 高速 基于

- 基于FPGA的光電抗干擾電路設計方案,光電靶的基本原理是:當光幕內的光通量發生足夠大的變化時,光電傳感器會響應這種變化而產生電信號。這就是說,一些非彈丸物體在穿過光幕時也會使得光幕內光通量發生變化以至光電傳感器產生電信號。從原理上,這種現

- 關鍵字:

電路設計 方案 抗干擾 光電 FPGA 基于

- 1引言直接數字頻率合成DDS(DirectDigitalSynthesizer)是基于奈奎斯特抽樣定理理論和現代器件生...

- 關鍵字:

FPGA DDS 信號源 設計

- 0引言現代信號處理技術通常都需要進行大量高速浮點運算。由于浮點數系統操作比較復雜,需要專用硬...

- 關鍵字:

高速流水線 浮點加法器 FPGA

- FPGA硬件系統的調試方法,在調試FPGA電路時要遵循一定的原則和技巧,才能減少調試時間,避免誤操作損壞電路。一般情況下,可以參考以下步驟進行FPGA硬件系統的調試。

(1)首先在焊接硬件電路時,只焊接電源部分。使用萬用表進行測試,排除電

- 關鍵字:

方法 調試 系統 硬件 FPGA

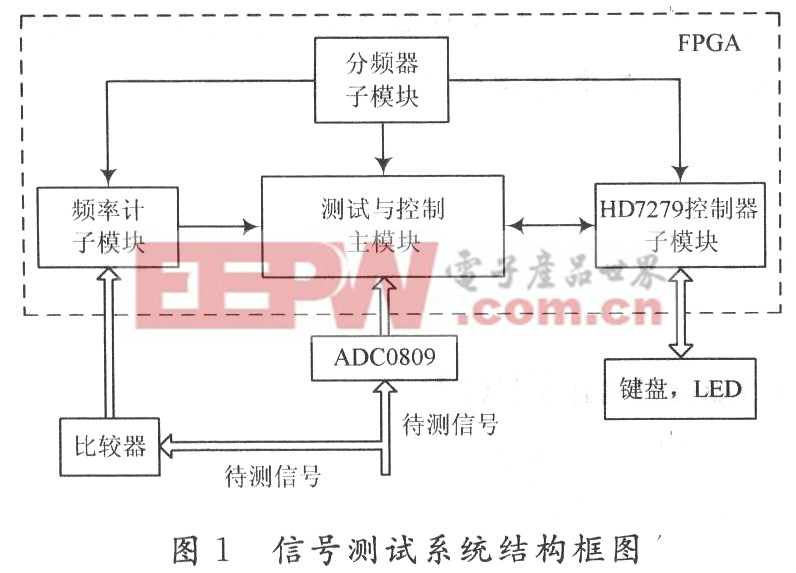

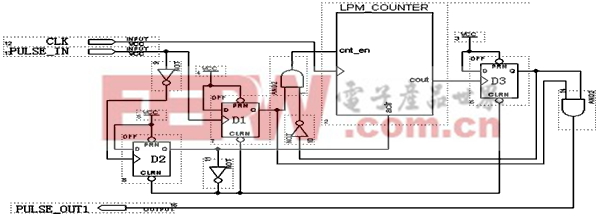

- 0引言數據采集和控制系統是對生產過程或科學實驗中各種物理量進行實時采集、測試和反饋控制的閉...

- 關鍵字:

FPGA 數據采集

soc-fpga介紹

您好,目前還沒有人創建詞條soc-fpga!

歡迎您創建該詞條,闡述對soc-fpga的理解,并與今后在此搜索soc-fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473