- ? 作為一個負責FPGA?企業市場營銷團隊工作的人,我不得不說,由于在工藝技術方面的顯著成就以及硅芯片設計領域的獨創性,FPGA?正不斷實現其支持片上系統設計的承諾。隨著每一代新產品的推出,FPGA?在系統中具有越來來越多的功能,可作為協處理器、DSP?引擎以及通信平臺等,在某些應用領域甚至還可用作完整的片上系統。 因此,在摩爾定律的作用下,FPGA?產業的門數量不斷增加,性能與專門功能逐漸加強,使得?FPGA?在電子系統

- 關鍵字:

xilinx FPGA VHDL Verilog

- ??? 全球可編程平臺領導廠商賽靈思公司?(Xilinx,?Inc.?(NASDAQ:XLNX)?)宣布推出其首批用于加速?28nm?7?系列FPGA系統開發與集成能力提升的目標設計平臺。賽靈思針對?FPGA?系統設計和集成的目標設計平臺方法提供了業界最全面的開發套件,包括開發板、ISE?設計套件工具、IP?核、參考設計和?FPGA?夾層卡&nbs

- 關鍵字:

Xilinx FPGA AMS

- 全球可編程平臺領導廠商賽靈思公司?(Xilinx,?Inc.)日前在進駐北京新址的慶典上,強調其對高增長的中國市場的承諾。該公司不斷擴大其在亞太地區的影響力,包括開設研發中心,并將本地銷售、市場營銷和應用工程設計等業務整合到統一的辦公地點。新址面積達?2,000?平米,將為北京本地、整個亞太區乃至跨國客戶提供強有力的支持。 從左至右,?北京化工大學教授何賓,?賽靈思軟件研發總監宋傳華博士,?全球研發高級總監Devadas,&nbs

- 關鍵字:

Xilinx 可編程平臺 FPGA,(AMS

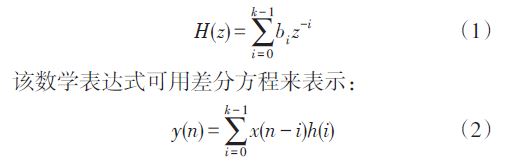

- 利用VHDL語言設計數字濾波器,主要在于如何實現乘法。乘法常用的實現方法有位串行乘法、分布式算法和并行乘法等。位串行乘法能節省大量硬件資源,但運算周期過長,對于數字濾波器這種高速率要求不宜采取。分布式算法是現在比較流行的一種乘法實現方式,所用硬件資源較少,運算速率也較快,但這只是針對小位寬乘法來說。對于數字濾波器的較大位寬的乘法,不宜采取。并行乘法,算法實現簡單直觀,對于現在資源豐富的FPGA,很好實現

- 關鍵字:

濾波器 數字 FPGA VHDL

- 0 引言

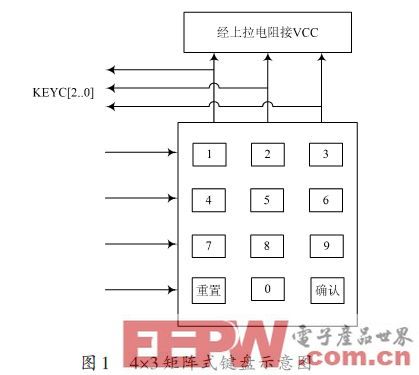

傳統機械鎖的防盜功能差,在現代高科技安防系統中無法起到作用,已逐步被更可靠、更智能的電子數字密碼鎖代替。目前市場上的大部分密碼鎖產品是以單片機為核心的,利用軟件進行控制,實際應用中系統穩定性較差且成本高。本文研究的是電子密碼鎖的一種純硬件實現方案,為彌補傳統技術的不足,采用EDA技術在可編程芯片上實現密碼的存儲、運算等操作,使產品既具有硬件的安全性和高速性,又具有軟件開發的靈活性和易維護性。

1 主要技術與開發環境

1.1 EDA技術及特點

EDA(Electronic Design A

- 關鍵字:

FPGA VHDL

- 在數字系統的設計中,FPGA+ARM的系統架構得到了越來越廣泛的應用,FPGA主要實現高速數據的處理;ARM主要實現系統的流程控制。人機交互。外部通信以及FPGA控制等功能。I2C、SPI等串行總線接口只能實現FPGA和ARM之間的低速通信; 當傳輸的數據量較大。要求高速傳輸時,就需要用并行總線來進行兩者之間的高速數據傳輸。

- 關鍵字:

FPGA ARM DATA VHDL 數據總線

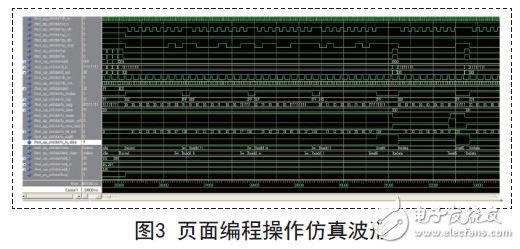

- 本文提出一個基于FPGA的SPI Flash讀寫硬件實現方案,該方案利用硬件對SPI Flash進行控制,能夠非常方便地完成Flash的讀寫、擦除、刷新及預充電等操作,同時編寫的SPI Flash控制器IP核能夠進行移植和復用,作為SOC芯片的功能模塊。

- 關鍵字:

FPGA Flash SOC CPU VHDL

- 在Matlab/Simulink環境下,采用DSP Builder模塊搭建FIR模型,根據FDATool工具對FIR濾波器進行了設計,然后進行系統級仿真和ModelSim功能仿真,其仿真結果表明其數字濾波器的濾波效果良好。

- 關鍵字:

DSP FPGA VHDL 濾波器 FIR

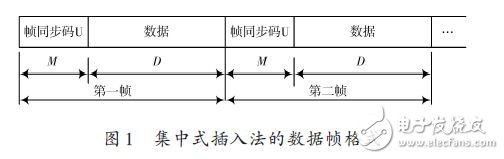

- 在Xilinx的FPGA器件XC3S200-4FT200上對方案中設計的幀同步系統進行了實現,利用Modelsim 6.0軟件進行了仿真測試。仿真結果表明,本方案設計的同步系統工作穩定,滿足性能要求。

- 關鍵字:

Xilinx FPGA 幀同步 VHDL 寄存器

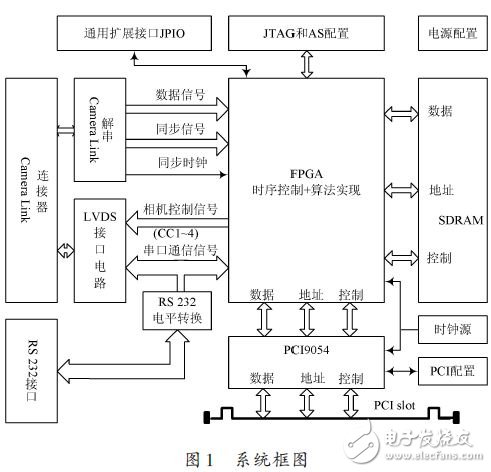

- 圖像在采集過程中不可避免地會受到傳感器靈敏度、噪聲干擾以及模數轉化時量化問題等因素影響而導致圖像無法達到人眼的視覺效果,為了實現人眼觀察或者機器自動分析的目的,對原始圖像所做的改善行為,就被稱作圖像增強技術。

- 關鍵字:

傳感器 圖像增強 FPGA PCI VHDL

- 文中詳細介紹了QPSK技術的工作原理和QPSK調制、解調的系統設計方案,并通過VHDL語言編寫調制解調程序和QuaitusII軟件建模對程序進行仿真,通過引腳鎖定,下載程序到FPGA芯片EP1K30TC144-3中驗證。軟件仿真和硬件驗證結果表明了該設計的正確性和可行性,由于采用FPGA芯片,減小了硬件設計的復雜性,該設計具有便于移植維護和升級的特點。

- 關鍵字:

VHDL QPSK 調制解調系統 設計與仿真

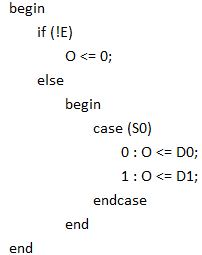

- 4.5.1 always塊語言指導原則使用always塊進行可綜合的代碼設計時需要注意以下幾個問題。(1)每個always塊只能有一個事件控制“@(event-expression)”,而且要緊跟在always關鍵字后面。(2)always塊可以表示

- 關鍵字:

VHDL 進階 代碼設計 邏輯

- 從大學時代第一次接觸FPGA至今已有10多年的時間。至今記得當初第一次在EDA實驗平臺上完成數字秒表,搶答器,密碼鎖等實驗時,那個興奮勁。當時由于沒有接觸到HDL硬件描述語言,設計都是在MAX+plus II原理圖環境下用74系列邏輯器件搭建起來的。

- 關鍵字:

FPGA EDA VHDL Verilog 時鐘 IP核

- 為了實現靶場時統終端輸出IRIG-B標準DC code信號,采用VHDL語言在FPGA邏輯電路中設計了DC code編碼器硬件電路,通過QuartusⅡ軟件建立工程文件對VHDL語言DC code編碼器電路進行編譯和仿真,獲得了符合IRIG-B標準的DC code信號。經過實踐驗證,該電路具有實現方法簡單、電路穩定性好、精度高的特點,實測同步精度小于1μs。

- 關鍵字:

IRIG-B FPGA code VHDL

vhdl-ams介紹

即IEEE 1076.1標準。

VHDL-AMS是VHDL的一個分支,它支持模擬、數字、數模混合電路系統的建模與仿真。

http://www.eda.org/vhdl-ams/

Verilog-AMS與之類似。支持模擬、數字、數模混合電路系統的建模與仿真。

http://www.eda.org/verilog-ams/

The VHDL-AMS language [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473