基于DSP和FPGA的通用圖像處理平臺設計

1 引言

本文引用地址:http://cqxgywz.com/article/104401.htm隨著數字化技術不斷發展和完善,數字圖像處理技術已廣泛應用于工業、軍事、生物醫療、電信等領域。實際應用中能夠運行復雜靈活的圖像處理算法和大數據量的數據傳輸處理能力成為圖像處理平臺穩定運行的前提,而系統實時性、體積、功耗等因素也至關重要。傳統數字圖像處理平臺大多采用通用PC機、高速圖像采集卡和基于VC++的軟件平臺來實現,但很難滿足當前對系統體積、功耗和實時性要求。因此這里提出的基于DSP和FPGA的通用圖像處理平臺,充分發揮FPGA靈活性強和DSP運算速度快、尋址方式靈活的優點,更好地提高圖像處理系統的集成度,降低系統功耗,并滿足實時性要求。

2 高速圖像處理平臺的工作原理

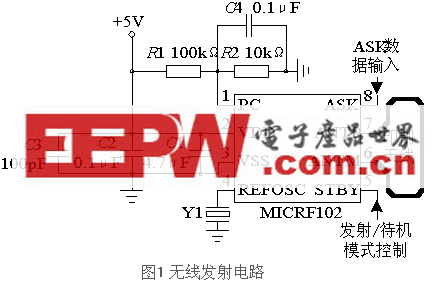

為實現高速圖像的實時處理,該系統采用DSP和FPGA線性流水線陣列結構,將FPGA可在通用接口設計和簡單信號處理等方面的優點與DSP的快速數字信號處理能力相結合,充分發揮這兩者的優點。該系統主要由DSP和FPGA的子系統構成,為保證大量圖像數據流快速穩定通訊,DSP與FPGA間通過外擴的SDRAM實現大容量數據交換。DSP子系統則實現較為復雜的圖像處理算法,并提供圖像存儲功能。而FPGA子系統完成CCD傳感器圖像數據的預處理以及微控制器通用接口功能。

系統結構原理圖如圖1所示。CCD傳感器輸入的圖像數據經FPGA預處理后,將數據傳送至DSP,DSP對輸入數據進行實時圖像處理,并將處理后的圖像通過EMIF接口發送并保存至外擴SDRAM。同樣,FPGA也能夠讀取外擴SDRAM的圖像數據,通過VGA接口實時顯示。對于少量數據流,如系統參數或圖像數據傳輸的起止信息等,則通過SPI接口實現。DSP子系統內部擴展有SD卡接口和USB主機接口,主要用于圖像數據的存儲和傳輸等。FPGA子系統外擴的主要接口包括:I2C、SPI、UART、PS/2和VGA等接口,用于系統升級和調試,提高系統通用性。

3 系統硬件結構設計

系統硬件設計采用模塊化設計思想,將整個系統分為DSP子系統和FPGA子系統。這兩者間的數據交換通過雙端口RAM方式實現。

3.1 器件選型

該系統設計選用TI公司的TMS320VC5509A型DSP。該款DSP功耗低,片上資源豐富,主頻最高可達200 MHz,片上帶有128 K×16 bit RAM和32 K×16 bit ROM,內置6個DMA通道,1個I2C接口,3個McBSP接口,1個RTC模塊,其外部存儲器接口(EMIF)能與SDRAM無縫連接,同時還帶有USB接口。FPAG選用ALTERA的Cyclone-II系列處理器,具有強大的邏輯處理能力,從而實現微處理器通用接口設計和簡單信息預處理功能。

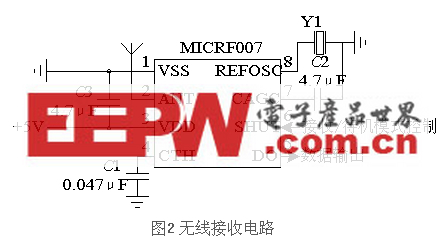

3.2 DSP與FPGA的接口設計

為保證系統實時性,DSP與FPGA之間的接口需實現大數據流通訊流暢的功能。將FPGA內部結果緩沖器模擬為SDRAM接口,一端輸入CCD圖像信號,一端輸出圖像數據并連接至DSP數據線。DSP的EMIF接口外接一片4 M×16 bit的SDRAM MT48LC4M16A2-75,通過將處理后的圖像數據回傳至外擴SDRAM,由FPGA實時讀取并通過VGA接口顯示,從而實現DSP與FPGA之間數據通訊功能。這兩者之間配置的雙端口RAM連接如圖2所示。

3.3 DSP子系統

DSP子系統主要包括電源管理單元、EMIF接口、SD卡接口、USB接口、JTAG調試接口和引導裝載(Bootload)電路等。電源管理單元主要為系統提供穩定電源;EMIF接口主要用于外部擴展存儲器;SD卡接口用于掉電后圖像數據的存儲;USB接口用于外接其他外設;JTAG接口用于電路調試等。

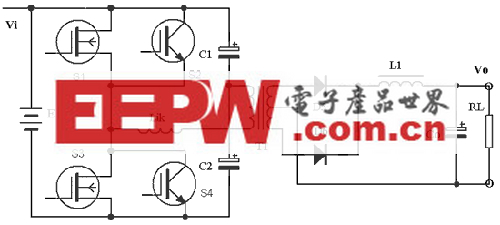

3.3.1 電源管理單元

DSP子系統供電可分為1.6 V和3.3 V兩種,DSP內核需1.6 V供電,外設及I/O端口采用3.3 V供電,并需保證內核先于I/O上電,I/O先于內核掉電。該系統采用電源器件TPS767D301配置不同電壓值。該器件包括兩路電壓輸出,每路最大輸出電流可達1 A.輸出電壓穩定。圖3為電源管理單元電路。

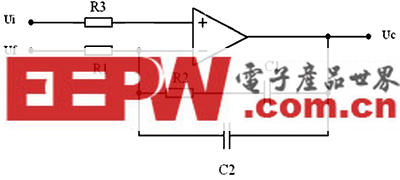

3.3.2 外部存儲器接口

TMS320VC5509A內部集成的EMIF接口除了支持異步存儲器,還支持同步突發靜態存儲器(SBSRAM)和同步動態存儲器(SDRAM)。在此通過編程寄存器配置EMIF和SDRAM的連接。設置CE空間控制寄存器1的MTYPE=011b表明連接存儲器是SDRAM。圖4為配置的4 M×16 bit的SDRAM MT48LC4M16A2-75的連接電路。由于單個CE空間的限制是4 MB,故使用2個CE空間,并將CEO引腳作為片選,CE1引腳懸空。外擴的SDRAM主要用于存儲處理后的圖像數據。

3.3.3 SD卡接口

TMS320VC5509A內置MMC控制器支持對MMC卡和SD卡的讀寫,支持MMC/SD協議和SPI協議,MMC控制器的運行頻率可通過程序設置,并與McBSP接口引腳復用,使用時需設置外部總線選擇寄存器(EBSR)。圖5所示為MMC控制器與SD卡信號連接圖,連接信號有:時鐘信號(CLK)、控制信號(CMD)和數據信號(DAT0~DAT3)。

3.3.4 Bootload電路

Bootload的功能是在系統上電后,將用戶程序從片外的慢速存儲器加載至片內RAM中,并使其高速運行。這里選用EEPROM作為外部非易失性程序存儲器。TMS320VC5509A的Bootload方式支持EMIF模式,SPI模式和McBSP模式等。其中SPI模式的EEPROM自舉有兩種,一種是基于16位字節地址,最大可達64 K尋址空間;另一種是基于24位字節地址,最大可達16 M尋址空間。在此選用第一種方式,并引出Bootload模式選擇引腳BOOTM[3:0],便于系統升級。

3.4 FPGA子系統組成及功能

為實現該圖像處理平臺通用性和實時性,FPGA子系統需實現的功能包括:開放式的圖像數據采集總線,DSP圖像處理實時數據總線,100 MB以太網接口,UART接口,VGA實時顯示模塊,I2C存儲器接口和PS/2接口等。其中UART接口方便系統軟件開發及調試,VGA接口用于圖像數據實時顯示,I2C接口外接EEPROM用于系統參數的掉電存儲。為實現多個系統的網絡化,FPGA子系統還設有以太網接口,用于多個系統將處理結果回傳至PC端口。PS/2接口為預留端口,后期根據需要增加鍵盤等輸入設備。

4 系統軟件設計

4.1 軟件開發開具

該系統軟件設計采用TI公司CCS3.1(Code ComposerStudio)作為開發環境,并利用CCS自帶的DSP/BIOS實時操作系統進行設計。在CCS中完成軟件的編輯、編譯、調試、代碼性能測試和項目管理等工作。通過使用DSP/BIOS提供的一系列豐富的內核服務,快速創建滿足實時性能要求的精細復雜的多任務應用程序。DSP/BIOS內核具有跨平臺的標準API接口,能被用戶程序調用,易于移植。此外,這些服務除支持多線程調度管理外,還支持系統實時分析以及資料管理。DSP/BIOS內核具有很大的尺寸伸縮性,多線程配置下的內核鏡像的代碼量最小僅有1 K字,占用DSP資源非常少。

4.2 軟件系統總體設計

在硬件平臺基礎上,利用CCS集成開發環境中的DSP/BIOS實時操作系統內核,開發具有可擴展性的軟件系統。系統軟件部分采用模塊化和層次化設計思想。軟件結構主要包括:設備驅動層、操作系統層、應用程序接口(API)層和應用層。設備驅動層負責與硬件有關的各個模塊或外設的驅動程序設計;操作系統層負責嵌人式實時操作系統移植;應用程序接口層完成系統控制功能、數據讀寫等,并實現硬件無關性;應用層則設計與系統應用背景有關的控制程序。圖6為系統軟件運行流程。軟件設計主要分為CCD圖像預處理后的接收任務、快速數字圖像處理任務、邏輯控制任務和圖像數據回傳任務。系統上電后,程序首先執行DSP的初始化和DSP/BIOS初始化,接著執行函數主體并啟動DSP/BIOS操作系統,以后的任務均由操作系統進行調度。采用嵌入式實時操作系統DSP/BIOS構建的圖像處理軟件平臺能較好滿足任務對實時性的要求,且結構穩定緊湊,可移植性高。

5 實驗結果

為驗證該系統的通用性與實時性,將其應用于某型號貼片機的器件檢測中,并進行以下3個實驗:DMA方式下大容量數據傳輸實驗,閾值分割測試實驗和模板匹配測試實驗。其中DMA方式下大容量數據傳輸實驗,通過DMA方式將片內數據傳輸至片外SDRAM內部,圖像大小為600×480字節。閾值分割和模板匹配實驗則直接讀取片外SDRAM中的圖像數據,并對圖像分別進行閾值分割和8×8模板匹配實驗,圖像處理算法采用TI公司圖像處理庫甬數。IMG threshold()和IMG_mad_8×8()。設置DSP運行時鐘為208 MHz,采用定時器0計時,DMA通道選用通道0,圖像數據大小為600×480字節。實驗結果如表1所示。

以上實驗數據表明,當采用600×480面陣CCD數據采集,并要求每幀圖像處理時間限定在30 ms以內時,該系統能很好滿足當前系統需要。

6 結論

系統能夠滿足600×480面陣CCD和普通線陣CCD傳感器對系統處理能力的需要,具有較強的通過性和實時性。其設計創新之處在于,充分運用DSP的強大運算能力和靈活的尋址方式,結合FPGA在通用接口設計和簡單信號處理速度方面的優點,采用基于DSP/BIOS的軟件架構,使得系統集成度高,功耗低,具備更高的實時性和可移植性。

評論