SDRAM接口時序和PCB布線長度的分析

引言

本文引用地址:http://cqxgywz.com/article/123975.htm經常看到有文章介紹對SDRAM布線的各種要求,這只是工程上的經驗總結,不同的芯片對時序的要求不同,對走線也有不同的要求,不能一概而論。其實,等長不是目的,真正的目的是滿足芯片的建立保持時間,采樣正確。由于FR4中的走線的傳播延時近似值為6英寸/ns,根據時序關系可以轉化為PCB Layout(印制板布局)的走線線長關系。

因為觸發器內部數據的形成是需要一定的時間的,如果不滿足建立和保持時間,觸發器將進入亞穩態,進入亞穩態后觸發器的輸出將不穩定,在0和1之間變化,這時需要經過一個恢復時間,其輸出才能穩定,但穩定后的值還不一定是你的輸入值。所以為了保證接口數據傳輸正確,必須滿足其建立保持時間。

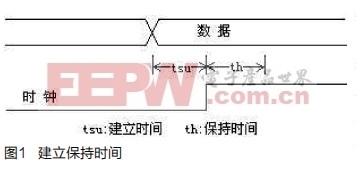

建立時間:觸發器在時鐘沿來到前,其數據輸入端的數據必須保持不變的時間。

保持時間:觸發器在時鐘沿來到后,其數據輸入端的數據必須保持不變的時間。見圖1。

其實觸發器的建立時間和保持時間比較短,為什么在接口的建立時間和保持時間卻較長呢?因為總線的影響,造成封裝和Die(芯片)中不同數據線傳播延時不同,需要滿足最快和最慢的數據線。另外時鐘信號在輸入芯片后,需要經過時鐘樹再傳到接口觸發器,造成時鐘的延遲可能比數據線更慢。這兩個原因造成接口信號的建立時間和保持時間需要有較多的冗余。我們研究接口的建立時間和保持時間,不需要關注芯片內部的延遲情況。

下面以SDRAM和DSP為例,說明SDRAM時序和PCB走線長度的關系。DSP為BF561,SDRAM為H57V2562GFR。SDRAM工作在133MHz,CL=3。

SDRAM和DSP接口時序分析

控制信號(單向)

建立時間應滿足:

tosu(DSP) + tClockRouteDelay – tControlRouteDelay(Slowest) ≥ t isu(SDRAM)

即:tControlRouteDelay(Slowest) – tClockRouteDelay ≤ tosu(DSP) – tisu(SDRAM)

評論