數字低通:名稱雖然不同 卻仍是一種濾波器

[Dave坐在實驗室中,凝視著充滿Verilog代碼的屏幕……]

T:你好Dave,現(xiàn)在你在做什么?!

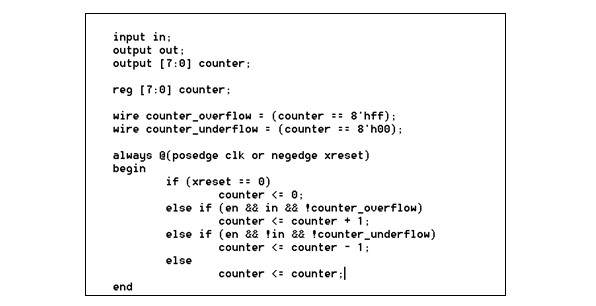

D:噢,你好T博士,這是一個新的芯片的印刷電路板(PCB)原型,它是一個混合信號芯片。我們正在構建一個FPGA的數字部分。FPGA的Verilog代碼看起來是這樣的。(Dave手指著屏幕。)

圖1:一個8位計數器的Verilog代碼片段

T:它看起來很像一個程序,像C代碼。是誰寫的所有這些代碼?

D:我們的一位首席工程師Warren Craddock,把這個放在一起,你是對的——雖然我不是專家,但我可以利用我以往在C語言方面經驗修改別人的代碼。一個很大的不同在于,軟件C代碼是由一個處理器執(zhí)行的,而Verilog語言被編譯成了硬件邏輯。他們說,Verilog是“并發(fā)的”(每個語句都是同時執(zhí)行,因為每個語句都有其自己的專用邏輯),而C代碼是“順序的”(語句是順序執(zhí)行的,這是因為只有一個處理器)。

T:很有意思,但你仍然只是工作在這些位(bit)上。你不可能真正地處理這些信號,對吧?

D:這是模擬設計師一種常見的誤解。的確,在大多數情況下,一個位并不能很好地代表一個模擬信號,即使你收集了進入一條總線一大堆位,它只代表一個數字。數字的數量隨著位的數量急劇增加,這樣8位就給了我256個選擇,而12位可以給我4000個選擇。

T:所以一條總線可以代表一個模擬信號,同樣,A-D轉換器代表了其輸出端的模擬輸入。時間和幅度都被量化了。

D:沒錯。一個8位轉換器可將0至2V輸入分成256個數字,并在每個時鐘周期生成一個數字。現(xiàn)在信號是一個數字流。

T:聽起來非常昂貴。你總得需要A-D和D-A轉換器。

D:不一定。我們可以從模擬信號開始——但我們不是必須那樣。我們可以在邏輯中內部生成信號,代表斜率、三角波、正弦波信號,等等。這些信號不一定能到達模擬世界,但我們可以用濾波器、調制器和峰值檢測器將這些信號處理得像模擬信號一樣。

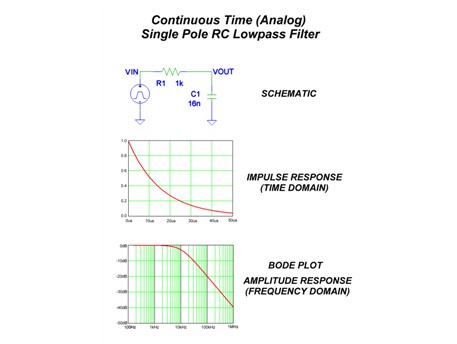

T:時間就是一個例子。我能想到的最簡單的濾波器是一個RC低通濾波器(LPF)。讓我來畫出電路和它的波特圖。

圖2:模擬RC的波特圖和脈沖響應

(圖字:連續(xù)時間(模擬)單極RC低通濾波器;原理圖;脈沖響應(時域);波特圖振幅響應(頻域))

評論