混合信號設計:模擬信號鏈的數式控制的優點

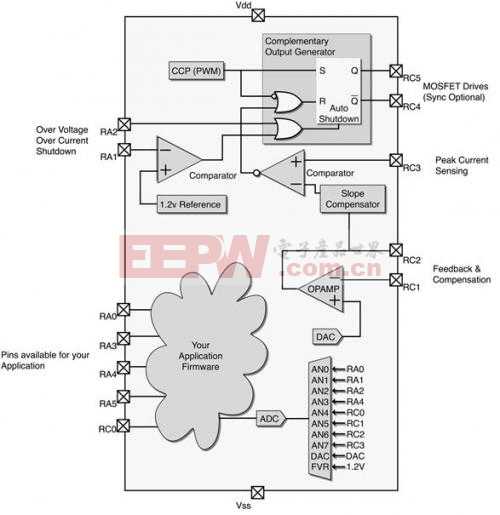

比較器是“數字信號分析儀”的最簡單例子,它以1.5伏參考電壓來比較輸出信號。信號將會被調幅,以便其最低值剛好可以開始解扣比較器。標記為IEC_Controller的塊包含數字控制算法。該控制器背后的基本思路是簡單的:

本文引用地址:http://cqxgywz.com/article/124441.htm1. 測量時鐘周期中比較器輸出為低的部分。

2. 周期性地將該部分與理想目標值進行比較。

3. 如果總數過高,則下調直流增益。如果過低,則上調直流增益。

該電路的其余部分是一個“顫振檢波器”,具體化于IEC_DitherDetector 塊中,它能夠確定直流增益值實現穩定的時間。穩定化過后,控制回路的輸出被鎖定。這可以防止電路在代碼間隨機漫游。

數字回路考慮

任何控制回路都必須有一個目標(值或試圖達到的條件),該AGC電路是按照每256個時鐘周期11個高比較器總數,或者約0.4%的占空比的明確目標來設計的。

只所以選擇該值是因為由此產生的誤差(0.4%)被認為是可以接受的。但由于應用情況各不相同,所以必須慎重選擇誤差信號的動態范圍。

使用稱為ComparatorCounter的計數器來進行比較器為高時的時鐘周期計數。控制回路通過用實際計數總數減去目標值來創建稱為Error的誤差信號。

回路輸出限制于不溢流或下溢。此外,每個更新事件都會清空ComparatorCounter,從而開始另一個256時鐘周期測量。

多反饋回路考慮

當控制回路是系統中的唯一控制回路時,其轉換行為在某種程度上是無關緊要的,但當其可能干擾多個其他回路時就會變得非常重要而必須加以考慮。

控制理論的一個眾所周知的結論是,當同時使用多個控制回路時,它們應當有不同數量級的時間常數,以便最小化它們之間的相互作用。

數字控制回路的時間常數非常容易改變。例如,如果回路輸出是N位寬,則誤差積分器可設計為若干位寬,比如N+2位。然后,最低有效位被視為小數且留下不用,從而有效地使回路慢下來。再使用一點額外邏輯還可以使時間常數動態化,亦即隨著其他回路的狀態而變化。

顫振和恢復

“顫振”一詞描述了控制回路在兩個(或更多)離散輸出碼之間來回振蕩的情形。這對這些類型的控制回路是正常行為,在一些應用中沒有什么重要意義。

在不容忍顫振的應用中,可以使用一點額外邏輯予以消除。檢測顫振最容易的方法是看回路的誤差信號。當誤差信號小時,回路接近其目標。當誤差信號在適合的時間長度內一直保持小,則可禁用回路的誤差積分器,以防止進一步更新。

確定誤差信號何時在“合適的時間”內一直保持小意味著某種低通濾波。最簡單的低通濾波器是單極IIR(無限脈沖響應)濾波器。這些濾波器易于以數字邏輯實現。

可使用另一個(可選)計數器來給予回路更多時間以便充分恢復,即使在其經濾波的誤差信號變小程度已經可接受之后。在本例中,該計數器稱為SettleCounter,無論何時,只要經濾波的誤差信號過大,其就會被清空。當經濾波的誤差信號小得可接受時,計數器向上計數,每個更新事件計一次。當計數器達到最大值時,控制回路的誤差積分器停止,回路的輸出不再變化。

回路本身繼續全時間運行(其誤差信號必須繼續跟蹤輸入信號中的變化),但輸出值被鎖定,因此其無法顫振。當輸入信號大幅變化時,經濾波的誤差信號將會增大,導致回路被解鎖并開始重新采集信號。

評論