如何讓7系列FPGA的功耗減半

本文引用地址:http://cqxgywz.com/article/127295.htm

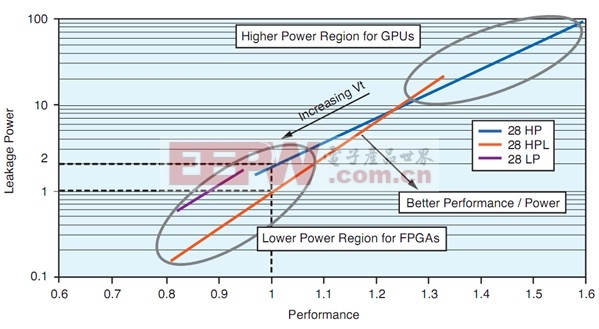

圖 2:28nm HPL 工藝、28nm 高性能 (HP) 工藝和 28nm 低功耗 (LP) 工藝的性能及漏電流對比

圖中文字:

漏電流

性能

GPU 的高功耗區域

增加 Vt

更高性能/功耗比

FPGA 的低功耗區域

7 系列還提供另一種稱為電壓 ID (VID) 的模式。客戶可以通過控制 Vcc 電壓和發揮部分器件的額外性能來降低功耗。每個器件都存有一個電壓 ID。這個可讀 VID 明確指出該器件在仍能滿足性能規范條件下可運行的最低電壓。

這種額外的余量令人振奮的是,為設計人員提供了更多選擇。Myron 說:“客戶可以選用 7 系列器件來實現他們現有的設計,同時讓現有設計的功耗減半。或者他們可以保持原有的功耗水平,為系統增加更多功能,直到達到余量。這樣可以降低系統總體功耗,節省板級空間,提高性能,同時大幅降低系統總成本。”

賽靈思 7 系列的所有 3 個 FPGA 產品系列和新推出的 ZynqTM-7000 可擴展處理平臺均采用這種專為 FPGA 優化的 HPL 工藝。賽靈思在這些器件的所有 FPGA 結構中均采用統一的方法(即基于小型高能效模塊的統一 ASMBLTM 架構)來處理。這樣客戶就能夠在所有這些器件系列中更輕松進行設計移植:低成本低功耗 ArtixTM-7 FPGA;具有業界最佳性價比的KintexTM-7;具有業界最佳性能和最大容量的 Virtex®-7;以及集成了嵌入式 ARM 雙核CortexTM-A9處理器,主要面向嵌入式應用的 Zynq-7000 可擴展處理平臺。

雖然同類 FPGA 競爭產品繼續采用 HP 工藝和 LP 工藝來實現單一架構的各種變體,但賽靈思堅信采用專為 FPGA 定制的工藝實現的統一芯片架構,可推動作為一種可編程平臺的FPGA 技術日趨成熟,在此,FPGA 芯片僅作為平臺的基礎,而不是系統解決方案的全部。按照隨 Virtex-6 和 Spartan®-6 FPGA 推出的賽靈思可編程平臺戰略,賽靈思提供的不僅是高級芯片,還包括特定市場開發板、專用開發板、IP 核、工具及技術文檔,有助于客戶迅速開展創新。

Myron 提到,轉向使用優化的工藝和統一架構,在半導體行業中并非史無前例或者是走極端,它只是把英特爾公司率先提出的、且在過去五年得到了成功部署的一套戰略用到 FPGA 上(見白皮書《在 Intel Core 微處理器架構內》)。

曾供職于英特爾公司的 Myron 表示:“2006 年,英特爾停止使用多種微處理器架構,采用單一芯片工藝實現了其功能最為強大的統一硬件架構 — Intel Core 微處理器架構,并將其應用于從高端計算服務器到移動筆記本產品等多個產品線。為什么像英特爾這樣看似有無窮資源可以利用的公司會專注于一種硬件架構?答案是他們只想做一件事,并把它做好。那就是集中資源打造出出色的統一架構:既可通過擴展用于滿足不同應用需求,同時還可讓客戶基本無需重新設計,就可以輕松地把同一架構用于多個應用。”

Myron 表示,對賽靈思來說當然也是如此。“通過為 7 系列 FPGA 選擇通用架構,我們可以讓我們的軟件工程隊伍專注于優化結果質量,無需分心于多個產品系列。無獨有偶,我們的客戶也強烈希望用類似的方式來優化 IP 核重用。與跨越多個不同的架構相比,維護統一架構有助于用最小的工作量實現 IP 核重用。”

fpga相關文章:fpga是什么

評論