如何讓7系列FPGA的功耗減半

—— 如何讓7系列 FPGA的功耗減半

在“降低靜態功耗”的發展歷程中,賽靈思采用高介電層金屬閘 (HKMG) HPL 工藝僅僅是邁出了第一步,而調整 7 系列器件架構,則又邁出一步。在此前的 FPGA 產品中,賽靈思允許用戶采用電源門控技術來關斷未使用的收發器、鎖相環 (PLL)、數字時鐘管理器和 I/O。而在 7 系列 FPGA 中,設計人員可以用同樣的方法來禁用未使用的 block RAM 模塊。由于block RAM 模塊的漏電流占給定器件總漏電流的 30% 之多,因此電源門控技術確實能起到明顯的效果。

本文引用地址:http://cqxgywz.com/article/127295.htm降低系統總功耗

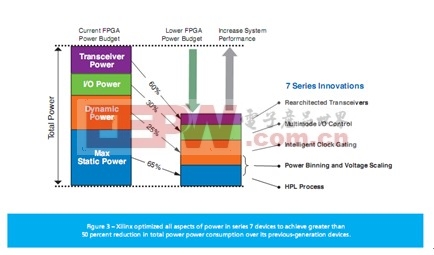

Myron 說,雖然選用高介電層金屬閘 (HKMG) HPL 芯片工藝已經顯著降低了靜態功耗和動態功耗,但賽靈思又進一步采取措施來減少 7 系列器件的系統總功耗,即從由靜態漏電流、動態功耗、I/O 功耗和收發器功耗組成的系統總功耗入手(見圖 3)。

圖 3 – 賽靈思通過優化 7 系列器件的各項功耗,使其相對前代器件而言,總功耗降低一半以上

圖中文字:

總功耗

目前 FPGA 功耗預算

較低的 FPGA 功耗預算

提高系統性能

收發器功耗

I/O 功耗

動態功耗

最大靜態功耗

7 系列創新

重新架構的收發器

多模 I/O 控制

智能時鐘門控

功率分級和電壓調節

HPL 工藝

fpga相關文章:fpga是什么

評論