時鐘抖動對光纖接入數字中頻系統的影響分析

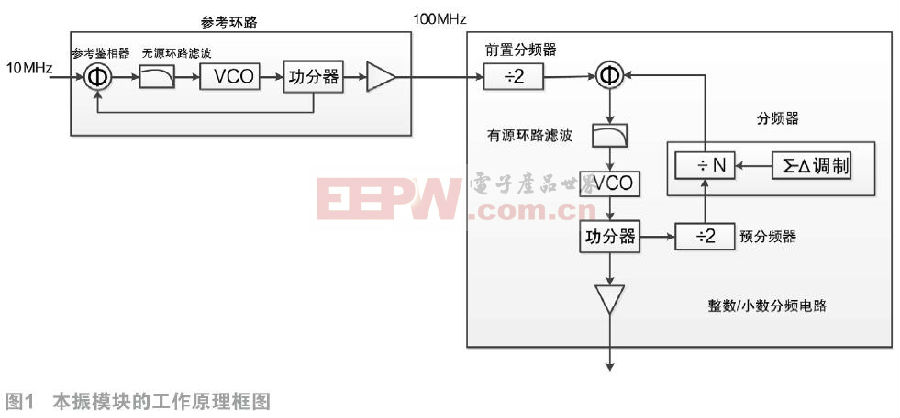

摘要:本文根據光纖接入數字中頻系統的時鐘使用情況,分析了時鐘抖動對ADC和鎖相環性能影響的原理,講述了鎖相環的基本原理和相噪優化方式,最后給出采用雙環鎖相環來完成去抖和時鐘分發的解決方案。

本文引用地址:http://cqxgywz.com/article/131701.htm時鐘相噪對ADC性能的影響分析

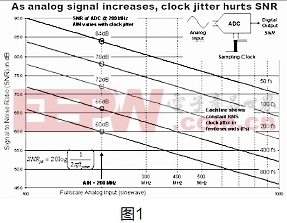

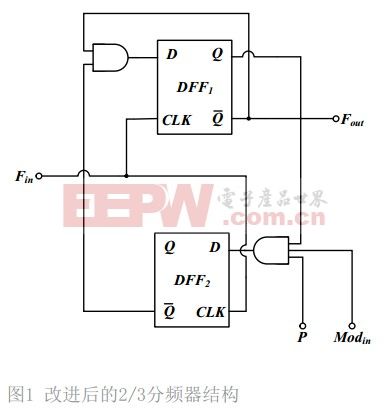

一款設計好的高速ADC,它的SNR基本是確定。到底需要多小的抖動才能夠滿足系統的ADC的需求呢?如圖1所示。不同輸入頻率,在不同抖動水平下,可以達到不同的最大SNR水平。舉例,當輸入頻率為200MHz,系統時鐘抖動為200fs水平時候,可以達到SNR水平就是72dB(如圖1虛線和綠色線交叉點)。

時鐘對鎖相環的影響分析

在數字中頻系統中,參考時鐘還會提供給鎖相環作為輸入參考頻率。而鎖相環的相噪好壞會影響到接收鏈路的EVM指標。

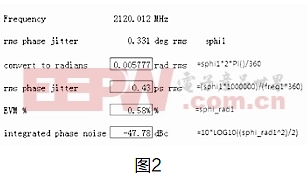

根據鎖相環輸出的相噪(抖動)水平和輸出頻率,可以通過下圖2的過程計算其對系統EVM的影響水平。因此我們可以得出結論:參考時鐘相噪影響鎖相環近端相噪,鎖相環近端相噪影響系統接收機的EVM指標。

評論