- 總體設計思路與框圖架構設計初期,首先完成了系統(接收機)與子系統(第一本地振蕩器)的全面分析,核心優先級聚焦低相位噪聲指標。隨后通過方案權衡,確定了合成器的總體技術路徑(直接式 MMD 或間接式 PLL)及所需的環路數量,最終選擇間接式 PLL 方案,核心考量如下:直接式 MMD 方案:相位噪聲更低、切換速度更快,但雜散抑制難度大,且尺寸、重量、功耗(SWaP)、成本與復雜度均較高;間接式 PLL 方案:相位噪聲與切換速度略遜于直接式,但雜散問題更易控制,且具備 SWaP 更優、成本更低、結構更簡單的顯著

- 關鍵字:

鎖相環 設計 202512

- 隨著 5G 向 6G 演進、衛星通信與毫米波技術普及,現代無線通信系統正朝著更高頻率、更寬帶寬、更復雜調制的方向飛速發展。無論是商業領域的地面無線網絡,還是軍事場景的戰術視距無線電,都對核心頻率源 —— 本地振蕩器(LO)提出了嚴苛要求:不僅要突破高頻甚至太赫茲頻段限制,更需具備超低相位噪聲、低雜散與快速調諧能力。在當前技術路徑中,直接式(混頻 - 倍頻 - 分頻,MMD)合成器雖能滿足高性能需求,但存在尺寸、重量、功耗(SWaP)過大及成本高昂、結構復雜等痛點。而間接式(鎖相環,PLL)合成器雖具備輕量

- 關鍵字:

鎖相環 高帶寬 低噪聲

- PLL解調器很受歡迎,易于實現,與許多其他FM解調器電路相比,具有優異的噪聲性能。在本文中了解它們是如何操作的。鎖相環(PLL)是一種負反饋系統,廣泛應用于現代通信系統中,用于載波和符號同步、頻率合成,并作為眾多數字解調器的核心組件。在本文中,我們將重點介紹用于FM解調的PLL。通過反饋解調器改善噪聲在我們討論PLL解調器之前,我們將考慮另外兩個電路,以便我們有一個比較的基礎。圖1(a)顯示了其中的第一個,一個使用RL電路作為鑒頻器的簡單FM解調器。如圖1(b)所示,RL電路在載波頻率(fc)附近表現出幾

- 關鍵字:

鎖相環,調頻解調

- 一站式定制芯片及IP供應商——燦芯半導體(上海)股份有限公司近日宣布成功研發出一款通用高性能小數分頻鎖相環(fractional-N PLL) IP,支持24bits高精度小數分頻,最高輸出頻率4.5Ghz,另外還支持擴頻時鐘(SSC)功能,可以為客戶提供多功能的小數分頻 PLL解決方案。PLL電路一般用于產生輸出頻率,輸出頻率值與PLL的參考輸入頻率呈倍數關系。小數分頻PLL通過頻率乘法比例的小數值,實現更精確的輸出頻率控制,從而提供更高精度和準確度的輸出頻率。SSC發生器是在一定頻率范圍內調制時鐘信號

- 關鍵字:

燦芯半導體 小數分頻 鎖相環 IP

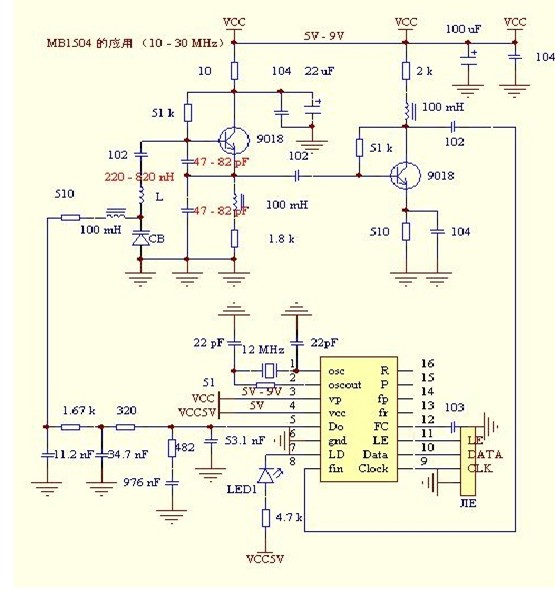

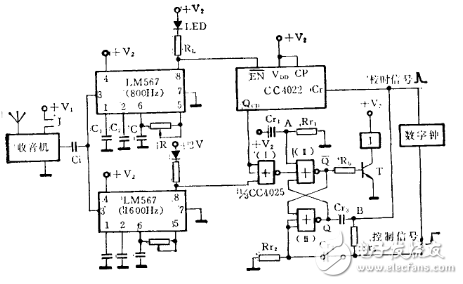

- 以下方案ARROW均有代理,被廣泛應用于多載波全球移動通信系統 (MC-GSM)、5G和毫米波無線基礎設施 、 微波回程連線 、測試和測量設備、高速數據轉換器計時、衛星通信等領域的頻率合成、時鐘產生和相位管理。同時ARROW可提供配套的底噪聲、高可靠性電源方案, 以及配套的高Q值感阻容器件,主要品牌有TI、ADI、NXP、ON、ST等。電路實解1. 鑒相器鑒相器是鎖相環路的關鍵部件。在頻率合成器中所采用的鑒相器主要有正弦波相位檢波器與脈沖取樣保持相位比較器兩種。1) 正弦波相位檢波器這種鑒相器實際上是一個

- 關鍵字:

鎖相環

- 永磁同步電機無傳感器控制方法由于具有降低成本、減小系統體積和提高可靠性等優勢,廣泛應用于軍工和民用等各個領域。本文介紹了用于零和低速下的永磁同步電機無傳感器控制技術。針對傳統的脈振高頻信號注入法轉子初始位置估計不準確的問題,提出一種基于磁極飽和凸機性的方法來正確判斷磁極極性。并通過數學算法將濾波環節進行簡化,減少低通濾波器的使用。通過仿真分析,驗證了所設計的脈振高頻電壓注入法在零和低速段的可行性。

- 關鍵字:

永磁同步電機 無傳感器控制 高頻信號注入法 鎖相環 202109 PMSM

- 鳳志民,杭孟荀(奇瑞新能源汽車股份有限公司,安徽 蕪湖 241002) 摘 要:為削弱傳統滑膜觀測器(Sliding Mode Observer, SMO)中由于控制函數的不連續性而引起的系統抖振,設計一種基于雙曲正切函數tanh的改進型SMO,采用截止頻率可變的策略對轉子位置角進行相位補償并且結合鎖相環估計轉子位置,在同步旋轉d - p 軸坐標系下建立和分析了改進型SMO,利用MATLAB/Simulink工具搭建改進SMO的仿真模型。仿真實驗結果表明:改進型SMO能有效削弱系統抖振,提高了轉子估

- 關鍵字:

202007 永磁同步電機 滑模觀測器 tanh函數 鎖相環 PMSM

- 本文基于TSMC 65 nm工藝設計出了一個高頻寬帶PLL,其中VCO模塊采用雙VCO架構、鑒頻鑒相模塊采用三態鑒頻鑒相器與電荷泵架構、環路濾波器采用二階低通無源濾波器、分頻器模塊采用整數N型架構。整個鎖相環輸出信號分辨率為100 MHz,工作范圍覆蓋26 GHz -41 GHz,且在28 GHz相位噪聲為 -124.2 dBc/Hz@10 MHz。

- 關鍵字:

鎖相環 寬帶 高頻 201902

- 顧名思義,鎖相環(PLL)使用鑒相器比較反饋信號與參考信號, 將兩個信號的相位鎖定在一起。雖然這種特性有許多用武之地,但是 PLL

如今最常用于頻率合成,通常充當上變頻器/下變 頻器中的本振(LO),或者充當高速 ADC 或 DAC 的時鐘。 或許,我們很少注意這些電路中的相位行為。但隨著對效率、帶寬和性能的需求日益增長,RF

工程師必須推出新技術來提高頻譜和功率效率。信號相位的重復性、可預測性和可調性在現代通信和儀器儀表應用中均起到日益重要的作用。 一切都是相對的 關于相位測量,如果不

- 關鍵字:

鎖相環 相位檢測

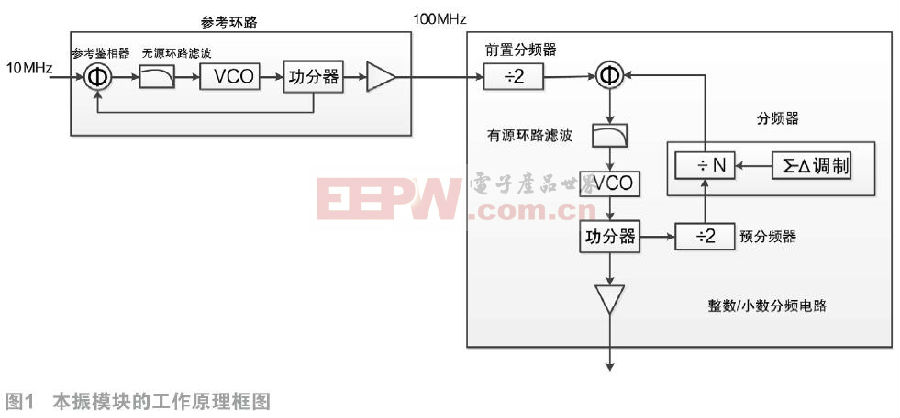

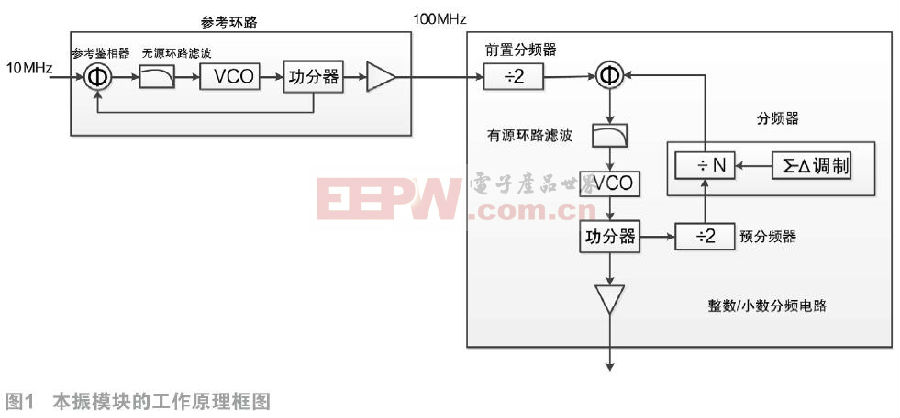

- 隨著移動通信的高速發展,矢量信號發生器和分析儀的需求越來越大,高性能寬帶本振的高造價成為制約兩種儀器成本的主要因素之一。利用壓控振蕩器(VCO)實現高性能寬帶本振設計,可以在降低模塊尺寸、降低模塊成本的前提下,實現高相噪、小型化的高性能本振。

- 關鍵字:

頻率合成器 鎖相環 寬帶 小型化 201807

- PLL和DLL:都是鎖相環,區別在哪里?-一般在altera公司的產品上出現PLL的多,而xilinux公司的產品則更多的是DLL,開始本人也以為是兩個公司的不同說法而已,后來在論壇上見到有人在問兩者的不同,細看下,原來真是兩個不一樣的家伙。

- 關鍵字:

鎖相環 DLL PLL

- PLL鎖相環的特性、應用與其基本工作過程-PLL(Phase Locked Loop),也稱為鎖相環路(PLL)或鎖相環,它能使受控振蕩器的頻率和相位均與輸入參考信號保持同步,稱為相位鎖定,簡稱鎖相。

- 關鍵字:

pll 鎖相環

- PLL鎖相環的基本結構及工作原理-PLL(Phase Locked Loop): 為鎖相回路或鎖相環,用來統一整合時脈訊號,使高頻器件正常工作,如內存的存取資料等。PLL用于振蕩器中的反饋技術。 許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步。

- 關鍵字:

pll 鎖相環

- 介紹一種針對FPGA優化的時間數字轉換陣列電路。利用FPGA片上鎖相環對全局時鐘進行倍頻與移相,通過時鐘狀態譯碼的方法解決了FPGA中延遲的不確定性問題,完成時間數字轉換的功能。

- 關鍵字:

時間數字轉換 鎖相環 FPGA

- FPGA的開發工具軟件,如Quartus II、ISE等,一般都會提供一些經過驗證的IP模塊。這些IP模塊是芯片廠家提供的,所以只能用于該廠家的FPGA芯片設計中。這些IP主要包括以下幾類。

- 關鍵字:

FPGA系統設計 存儲器 IP模塊 鎖相環 高速串行收發器

鎖相環介紹

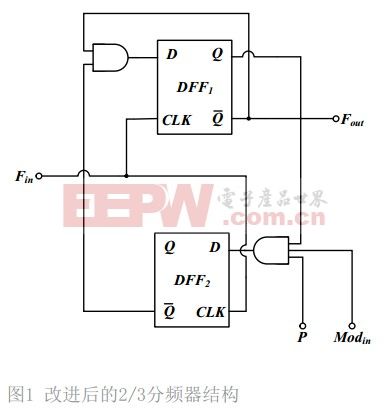

能使受控振蕩器的頻率和相位均與輸入信號保持確定關系的閉環電子電路。鎖相環的基本結構如圖1,其中鑒相器用來鑒別輸入信號ui與輸出信號u0之間的相位差,并輸出誤差電壓ud。ud中的噪聲和干擾成分被低通性質的環路濾波器濾除,形成壓控振蕩器(VCO)的控制電壓uC。uC作用于壓控振蕩器的結果是把它的輸出振蕩頻率f0拉向環路輸入信號頻率fi,當二者相等時,環路被鎖定,稱為入鎖。維持鎖定的直流控制電壓由鑒相器 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473