- 圖3.24給出了CADILLAC時鐘相位調整電路的框圖。對于大規模生產測試,可能值得構造這樣的電路。對于普通的實驗測試,則太麻煩了。電路將總線時鐘進行N分頻,然后通過一個-頻率比較器把它與一個同樣經過N分頻的本地振蕩

- 關鍵字:

鎖相環 時間調整

- 電路的功能很多電路都要求把頻率準確地倍增,使用PLL電路可很容易組成滿足這種要求的電路。例如主振頻率為1KHZ,若使用倍增器內插10個脈沖,可變成10KHZ的脈沖信號。在VCO中,即使主振頻率發生變化,也能獲得跟蹤主振

- 關鍵字:

PLL 10 IC的 鎖相環

- 摘要:延時鎖相環(DLL)是一種基于數字電路實現的時鐘管理技術。DLL可用以消除時鐘偏斜,對輸入時鐘進行分頻、倍頻、移相等操作。文中介紹了FPGA芯片內DLL的結構和設計方案,在其基礎上提出可實現快速鎖定的延時鎖相環

- 關鍵字:

FPGA 延時 鎖相環

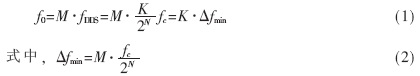

- 摘要:敘述了全數字鎖相環的工作原理,提出了應用VHDL 技術設計全數字鎖相環的方法,并用復雜可編程邏輯器件CPLD 予以實現,給出了系統主要模塊的設計過程和仿真結果。0 引言全數字鎖相環(DPLL) 由于避免了模擬鎖相環存

- 關鍵字:

VHDL 全數字 電路設計 鎖相環

- 該應用筆記討論了鑒頻鑒相器的指標對鎖相環(PLL)死區及抖動性能的影響。在使用電荷泵環路濾波的PLL設計中,通過產生具有最小脈寬的鑒相輸出脈沖,可以減輕PLL的死區效應和相關的鎖相環抖動。 鎖相環廣泛用于電信行業

- 關鍵字:

9382 MAX 鎖相環 中的應用

- 0 引 言

電荷泵鎖相環是閉環系統,系統各個部分都是一個噪聲源,各部分噪聲的大小不僅與電路本身有關,而且還與環路帶寬等因素有關。因此,設計時必須分析其各頻率范圍內噪聲源影響力的大小,權衡確定環路帶寬與

- 關鍵字:

鎖相環 環路帶寬 分析 相位噪聲

- 1.系統組成

語音/文字短信無線發射機的系統方框圖如圖1所示,由集成電路MC1648、MC145152、MC12022、低通濾波器和晶振構成鎖相環頻率合成器、音頻處理器、數據編碼器、AT89S52單片機、按鍵、128×64點陣型LCD等部分

- 關鍵字:

發射機 設計 無線 短信 文字 語音 無線電發射機 鎖相環 編碼器 單片機

- 本文用鎖相環頻率合成器專用芯片MC145152及其外圍電路設計了909~915 MHz步進25 kHz的頻率合成器,該頻率合成器具有較低的相位噪聲、很高的頻率穩定度,大大促進了數字鎖相頻率合成器集成化程度的提高和體積的縮小,滿足了通信設備的高集成度和超小型化的要求,特別適合某些特殊場合的應用。

- 關鍵字:

鎖相環 頻率合成器 方案

- 1 引 言 鎖相環是一種能使輸出信號在頻率和相位上與輸入信號同步的電路,即系統進入鎖定狀態(或同步狀態)后,震蕩器的輸出信號與系統輸入信號之間相差為零,或者保持為常數。傳統的鎖相環各個部件都是由模擬電

- 關鍵字:

全數字 分析 鎖相環

- 簡單介紹了全數字鎖相環(ADPLL)的結構和工作原理,提出一種在FPGA的基礎上可增大全數字鎖相環同步范圍的設計方法,并給出了部分verilog HDL設計程序的代碼和仿真波形。

- 關鍵字:

FPGA 全數字 鎖相環

- 摘要: 介紹了一種超寬帶雷達信號波形產生器的設計與實現,信號由DDS+PLL+混頻器產生。該產生器采用高性能數字鎖相環芯片Q3236、壓控振蕩器Q3500-0916T和混頻器IAM-81008構成核心單元,利用新型低頻和超帶寬帶通濾波器完成超寬帶雷達信號。這種超寬帶雷達信號的實現對提高現有雷達的性能以及研制新一代高性能雷達都具有重要意義。

關鍵詞: 超寬帶 直接數字合成 鎖相環 混頻器 濾波器

雷達是對遠距離目標進行無線電探測、定位、測軌和識別的電子設備,無論對軍用還是對民用,都占據重要位

- 關鍵字:

超寬帶 直接數字合成 鎖相環 混頻器 濾波器

- Maxim推出基于晶體的鎖相環(PLL) VHF/UHF發送器MAX7057,能夠在較寬的頻率范圍內發送OOK/ASK/FSK數據。器件配合適當的晶體頻率,可以發送300MHz至450MHz范圍內的任何信號,并能夠以高達100kbps的速率發送NRZ碼(50kbps曼徹斯特碼)。

MAX7057集成了可編程分數N PLL合成器和寬帶VCO,因而具有極大的靈活性。此外,還可以設置內部電容,實現功率放大器(PA)與天線之間的阻抗匹配。這種拓撲結構可確保多個工作頻率下的高效率傳輸,從而使MAX7057

- 關鍵字:

Maxim PLL 鎖相環 發送器

- 近年來誕生了許多種類的脈寬調整電路。這些電路大致可以分為以下三類:第一類最為簡單,即采用2分頻器產生占空比為50%的時鐘,2分頻器并不是專為調整占空比而采用的,但的確達到了這一需求;第二類通過負反饋機制,采用數字或模擬控制,調整信號占空比,這類電路最主要考慮的是系統穩定性;最后一種是采用復雜數字算法的占空比調整電路,其實現相對比較復雜。因此本文主要分析設計前兩種類型的脈寬調整電路。

- 關鍵字:

應用于 鎖相環 脈寬 調整電路

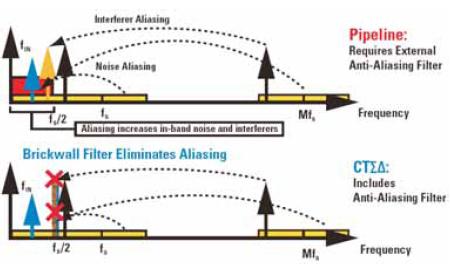

- 連續時間SD調制器

第一枚獲業界公認的SD調制器誕生于1962年,而它事實上是采用了CT電路。此后,利用CT電路來實現SD調制器便愈來愈普遍,但當開關電容器(SC)電路面世后,大部分的SD調制器都改以DT環路濾波器來實現。SC電路之所以受歡迎,原因是它不會受信號波形特性的影響。此外,SC積分器的時間常數可隨著采樣頻率而調整,從而提高系統的靈活性。可是,其后CTΣΔ調制器又因其某些優點而重新受到注視,例如是它采用較低功耗的積分放大器,以及內置有采樣輸入模/數轉換器沒有的抗混疊濾

- 關鍵字:

轉換器 CTΣΔ調制器 鎖相環 采樣時鐘 NI 200806

鎖相環介紹

能使受控振蕩器的頻率和相位均與輸入信號保持確定關系的閉環電子電路。鎖相環的基本結構如圖1,其中鑒相器用來鑒別輸入信號ui與輸出信號u0之間的相位差,并輸出誤差電壓ud。ud中的噪聲和干擾成分被低通性質的環路濾波器濾除,形成壓控振蕩器(VCO)的控制電壓uC。uC作用于壓控振蕩器的結果是把它的輸出振蕩頻率f0拉向環路輸入信號頻率fi,當二者相等時,環路被鎖定,稱為入鎖。維持鎖定的直流控制電壓由鑒相器 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473