基于DSP開發系統設計與實現

TPS767D301的輸出端1OUT的電壓由式(1)確定:

Vo=Vref(1+R1/R2) (1)

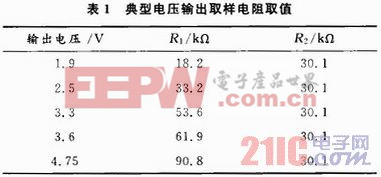

式中:Vref=1.183 4 V為電壓調整器的內部參考電壓;R1和R2的取值應保證驅動電流近似為50μA。如果電阻過小,會使電流過大,消耗電力;如果電阻過大,FB引腳會出現電流脈沖尖峰,會使輸出電壓波動。典型電壓輸出時,R1和R2的取值如表1所示。本文引用地址:http://cqxgywz.com/article/149182.htm

為了提高輸出電壓的穩定性,模擬電源與數字電源之間通過鐵氧體磁珠和電容進行濾波,鐵氧體磁珠具有可以忽略的寄生電容,電氣特性和一般的電感相似,這樣可以減少來自模擬電源或其他并聯電路所產生的噪聲生干擾。

2 系統RAM擴展

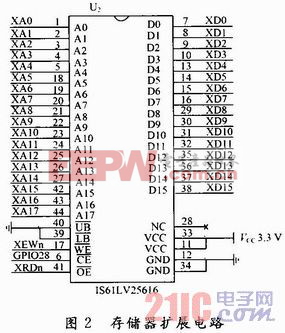

在TMS320F28335的片上已經集成了34 K×16 b的RAM,且內部RAM的訪問速度可達150 MIPS,通常用于放置系統對運算速度要求較高的程序。F28335的片上還集成了256 K×16 b的FLASH,但由于FLASH燒寫次數有限,而且燒寫速度慢,操作麻煩。使用外擴RAM后,仿真時程序可以放入外擴RAM中運行,程序長度不受限制,這樣程序的設計和調試就非常方便。在調試完成后通過修改.cmd文件等方法將程序燒進FLASH中運行。同時,外擴RAM還可以開放給其他任務。外擴RAM選用ISSI公司的IS61LV25616,存儲容量為256 K×16 b,3.3 V的供電電壓。使用區間6作為外擴存儲區間,存儲地址范圍為0x100000~0x13FFFF。由于IS61LV25616的訪問速度有8 ns,10 ns,12 ns,15 ns可選擇,而當CPU運行在150 MHz時,地址和數據的最小有效時間為3個時鐘周期,即20 ns,所以不用考慮時序問題。存儲器的地址線和數據線分別對應DSP的地址線和數據線,片選端CS和DSP的GPIO28連接,存儲器的讀/寫端口分和DSP的讀/寫端口連接,具體電路圖如2所示。

評論