基于FPGA的可重構智能儀器設計

2.3 可重構配置文件生成

在完成可重構智能儀器的各個控制器核之后,要生成相應的配置文件,才能配置FPGA 芯片,使其實現各種功能。

配置是對 FPGA 的內容進行編程的一個過程。目前大部分FPGA 都是基于SRAM 工藝 的,而SRAM 工藝的芯片在掉電后信息就會丟失,需要外加專用配置芯片,在上電時,由 這個專用配置芯片把配置數據加載到FPGA 中,之后FPGA 就可以正常工作了。

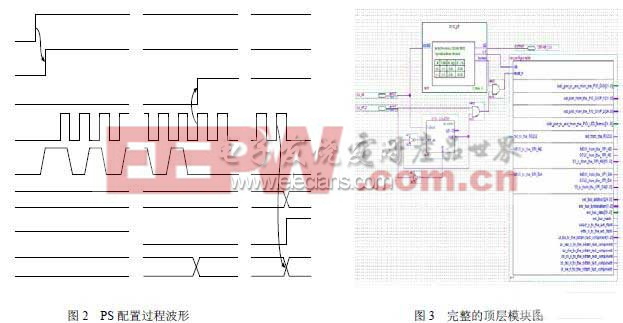

在被動模式(PS)方式下,FPGA 處于完全被動的地位。FPGA 接收配置時鐘、配置命 令和配置數據,給出配置的狀態信號以及配置完成指示信號等。PS 配置時序如圖2 所示:

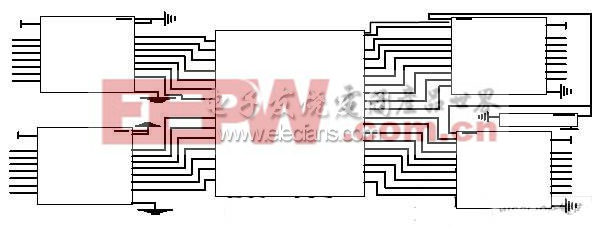

根據 SOPC Builder 中對FPGA 添加的各種控制器核,利用Quatus II 軟件例化Nios II 處 理器,生成了完整的FPGA 內部頂層模塊圖,如圖3 所示。然后利用引腳規劃器Pin Planner 對其進行引腳分配。最后用進行Compilation,生成.sof 和.pof 配置文件,完成硬件設計。

2.4 外圍電路設計

外圍電路設計包括存儲器設計、AD 轉換電路設計、DA 轉換設計、顯示電路設計、開 關量DI、DO 設計和RS232 通信設計等。

儀器上的存儲器包含 1 片8M 字節的SDRAM 和一片32M 字節的FLASH 存儲器。限于 篇幅SDRAM(IS42S16400)與EP2C35F672C6 連接的引腳、FLASH 存儲器(AT49BV163) 與EP2C35F672C6 連接的引腳分配這里不再贅述。

A/D 轉換電路采用了AD7810 芯片、DA 轉換電路采用AD5611 芯片。

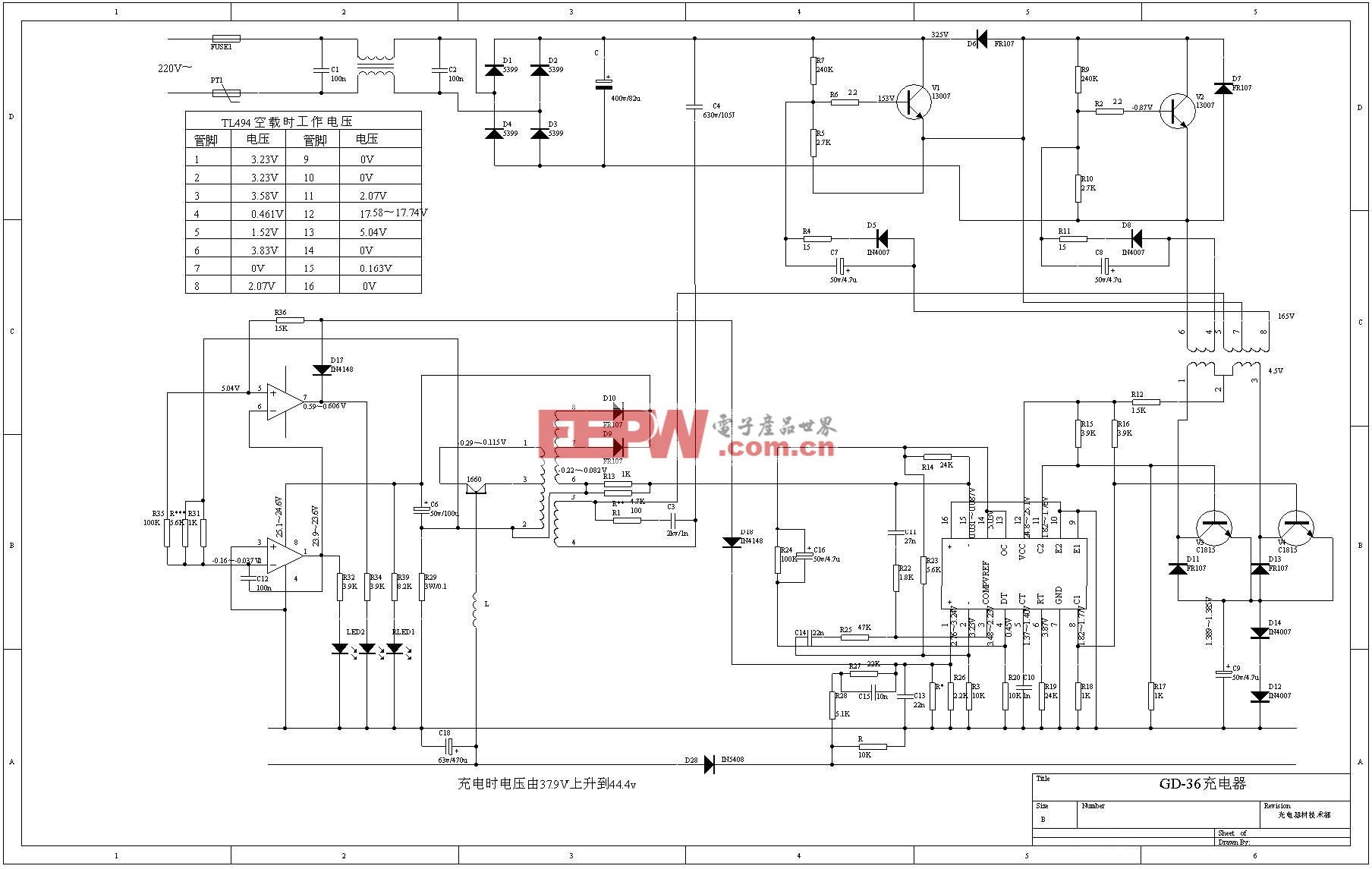

DI、DO 均為16 路,數字端口滿足標準TTL 電氣特性。數字量輸入最低的高電平為2V, 數字量輸入最高的低電平為0.8V;數字量輸出最低的高電平為3.4V,數字量輸出最高的低 電平為0.5V。DI、DO 部分的電路如圖4 所示:

評論