基于FPGA的高光效LCD投影機設計

① 通過模塊調用將FPGA的片內RAM分為“RAM_A”和“RAM_B”;

② 在第一個行周期,將輸入的第一行數據流緩存到“RAM_A”:因為一行視頻信號有3K字節,為了實現在LCD屏上三基色的分離,在對數據進行存儲時,不能按照數據進入FPGA的順序來存儲,而應將紅色數據依次存放在第1至第1024個存儲單元,綠色數據存放在第1025至第2048個存儲單元,藍色數據則放在第2049至第3072個存儲單元,即將原來的象素“打亂”存放;

③ 在第二個行周期,按照步驟②中所描述的方法將第二行的視頻信號存入“RAM_B”,同時將“RAM_A”中所存的第一行視頻信號依次從I/O口讀出,再經DVI編碼芯片編碼后送至LCD屏,即在讀出數據時“按序”讀取;

④ 重復步驟②、③,使讀、寫操作交替在“RAM_A”和“RAM_B”間循環進行,直至一幀數據傳輸完畢。

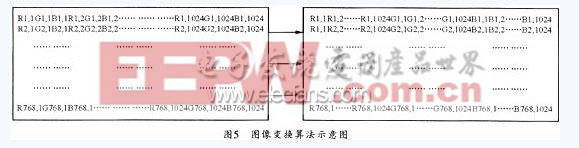

此時,LCD屏上顯示數據的具體算法如圖5所示,即R1,2占據G1,1的位置(即第2個單元),R1,3占據B1,1的位置(即第3個單元),R1,4占據第4個單元,以此類推,直至1024個紅色數據在LCD屏上排列完畢,再開始綠色數據,繼而是藍色數據。這樣便可達到圖2中在一塊LCD屏上分別顯示R、G、B圖像的目的。

本設計中所采用的FPGA是Altera公司CvclONe系列中的EP1C6Q240C8。該FPGA的片內存儲器容量為90kbits,完全能夠勝任對分辨率為XGA顯示模式的視頻信號進行行處理。如果要支持更高分辨率的投影模式或對圖像進行整幀的處理,只需更換具有更大片內RAM資源的FPGA或是在FPGA的I/O口外接片外存儲器。DVI解碼和編碼芯片分別選用Sil161和Sil164。

這種基于FPGA的控制器除可用投影機的視頻信號處理外,還可應用于平板顯示中有關圖像的翻轉、截取以及象素的抽取等。其操作的關鍵是對數據讀、寫地址的控制。

3 液晶屏的處理和光學調整

現在市面上的TFT液晶板都是有濾色膜的。本設計如果直接使用這種液晶板,那么當R、G、B三單色光分別照射到R、G、B圖像區域的時候,濾色膜會吸收掉很大一部分光能,從而從投影亮度過低,無法達到應用要求。因此,本設計中所采用的液晶板需去掉濾色膜或者沒有濾色膜的產品,以提高光源利用率和投影亮度。

由于視頻信號在LCD屏上分為R、G、B三個部分,因此,三基色圖像通過液晶板匯聚以后,會形成一幅高度和原圖像相等。寬度壓縮為原圖像三分之一的彩色圖像。這時,只需要一枚寬銀幕鏡頭即可將該壓縮圖像拉寬,從而使其恢復到正常圖像。

4 結束語

隨著家庭影院概念的普及,約來越多的消費者希望在家中享受大制作影片所帶來的強烈震撼。然而,昂貴的投影機卻讓很多家庭望而卻步。本文從實際應用出發,設計了一種基于FPGA的高光效單片彩色LCD投影方式。不難看出,該投影系統將具有如下優勢:

(1) 一旦產業化,這種新型投影機的成本比其它的LCD投影機要低很多,因而易于進入普通家庭;

(2) 集成度高,體積小,信息容量大,速度快;

(3) 光利用率顯著提高,從而提高了顯示質量。

評論