微處理器的低功耗芯片設計技術詳解

隨著半導體工藝的飛速發展和芯片工作頻率的提高,芯片的功耗迅速增加,而功耗增加又將導致芯片發熱量的增大和可靠性的下降。因此,功耗已經成為深亞微米集成電路設計中的一個重要考慮因素。為了使產品更具競爭力,工業界對芯片設計的要求已從單純追求高性能、小面積轉為對性能、面積、功耗的綜合要求。而微處理器作為數字系統的核心部件,其低功耗設計對降低整個系統的功耗具有重要的意義。

本文引用地址:http://cqxgywz.com/article/150405.htm本文首先介紹了微處理器的功耗來源,重點介紹了常用的低功耗設計技術,并對今后低功耗微處理器設計的研究方向進行了展望。

1 微處理器的功耗來源

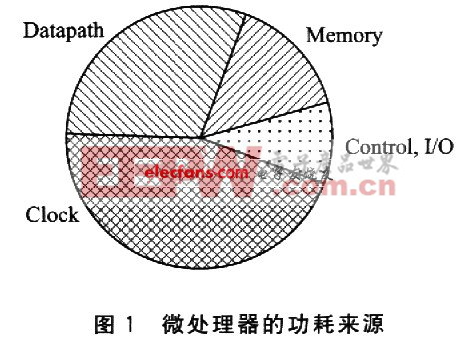

研究微處理器的低功耗設計技術,首先必須了解它的功耗來源。高層次仿真得出的結論如圖1所示。

從圖1中可以看出,時鐘單元(Clock)功耗最高,因為時鐘單元有時鐘發生器、時鐘驅動、時鐘樹和鐘控單元的時鐘負載;數據通路(Datapath)是僅次于時鐘單元的部分,其功耗主要來自運算單元、總線和寄存器堆。除了上述兩部分,還有存儲單元(Memory),控制部分和輸入/輸出 (Control,I/O)。存儲單元的功耗與容量相關。

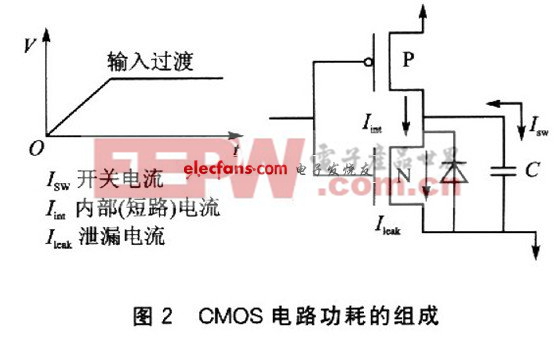

如圖2所示,CMOS電路功耗主要由3部分組成:電路電容充放電引起的動態功耗,結反偏時漏電流引起的功耗和短路電流引起的功耗。其中,動態功耗是最主要的,占了總功耗的90%以上,表達式如下:

式中:f為時鐘頻率,C1為節點電容,α為節點的翻轉概率,Vdd為工作電壓。

p2p機相關文章:p2p原理

評論