雙CPU數據處理系統設計

2.2.1 自舉引導過程

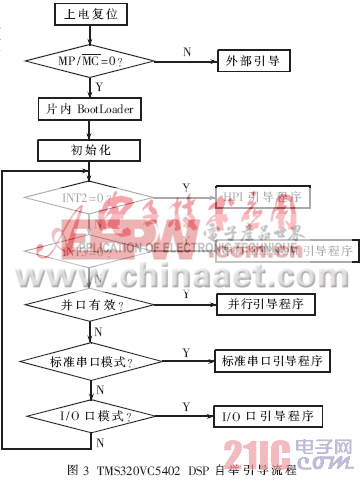

TMS320VC5402 DSP的引導加載選擇過程如圖3所示。系統上電或硬件復位后,首先判斷芯片的 引腳。如果該

引腳。如果該 引腳為高電平,則選擇微處理器模式,片內ROM從程序空間移去,DSP執行FF80H處的跳轉命令,跳轉到F800H處的引導程序段并實現代碼移植功能,如果引腳為低電平,則選擇微計算機模式,片內ROM被映射到程序存儲器空間,DSP執行FF80H處的跳轉命令,自動跳轉到內部引導程序入口地址F800H,啟動內部引導程序,選擇引導模式。本系統的

引腳為高電平,則選擇微處理器模式,片內ROM從程序空間移去,DSP執行FF80H處的跳轉命令,跳轉到F800H處的引導程序段并實現代碼移植功能,如果引腳為低電平,則選擇微計算機模式,片內ROM被映射到程序存儲器空間,DSP執行FF80H處的跳轉命令,自動跳轉到內部引導程序入口地址F800H,啟動內部引導程序,選擇引導模式。本系統的 引腳置低。

引腳置低。

圖3為DSP自舉加載的流程,上電判斷 為0后,依次檢測INT2、INT3,當滿足要求且并口有效時,即開始執行并行引導程序。否則,按引導流程依次判斷,直到滿足條件為止。

為0后,依次檢測INT2、INT3,當滿足要求且并口有效時,即開始執行并行引導程序。否則,按引導流程依次判斷,直到滿足條件為止。

2.2.2 實現自舉硬件接口電路的設計

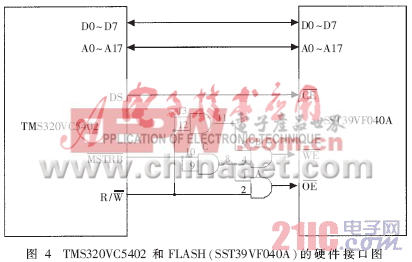

根據設計的需要,FLASH采用TI公司的SST39VF040A。圖4為TMS320VC5402和FLASH的硬件接口電路[5]。由于TMS320VC5402和FLASH都是3.3V供電,接口中TMS320VC5402的D0~D7直接與FLASH的D0~D7相連,二者的地址信號線A0~A17也相連,TMS320VC5402的DS接FLASH片選端CE,TMS320VC5402的和經邏輯組合后接FLASH 和

和 經邏輯組合后接FLASH的

經邏輯組合后接FLASH的 。

。

評論