圖像的二維提升小波變換的FPGA實現

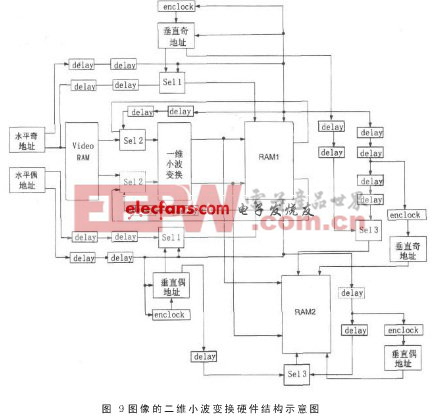

系統頂層原理如圖9所示(圖中略去了時鐘信號控制線)。在系統結構中添加delay延時寄存器,從調整系統的時序;RAM1、RAM2是沒有被放入初始化文件的兩個相同的存儲器;sel1、sel2、sel3是三類相似功能的數據選擇器,完成整個結構的基本控制功能。sel1實現的功能是當行變換結束后,切換RAM1的地址輸入為列方向地址;sel2實現的功能是當行變換結束后,將“小波變換”模塊的輸入數據從行變換地址尋址得到的數據切換到列變換地址尋址得到的數據;sel3實現的功能是通過行變換標志信號和列變換標志信號來實現對RAM2的讀寫控制,當系統進行列變換時,RAM2模塊寫無效;當系統進行列變換時,RAM2模塊寫有效;當列變換完成時,RAM2模塊再次寫無效,此時RAM2中已經寫入數據。

系統工作過程如下:首先是行方向一維小波變換:圖像的灰度值數據預存在“Video RAM”模塊中,時鐘信號一來,便立即啟動水平奇地址模塊和水平偶地址模塊,開始奇偶地址分裂,進行行方向的一維小波變換,同時將行變換的數據存到RAM1中。其次再進行行、列變換切換時控制:當一次行方向地址奇偶分裂一結束,水平奇地址模塊和水平偶地址模塊將發出一個結束的標志信號,它將啟動sel1、sel2、sel3開始工作。最后再進行列變換的過程,RAM2中存儲列變換的結果數據。此時即完成了圖像二維提升小波變換。

采用QuartusⅡ軟件對系統進行了綜合、仿真,系統在FPGA芯片中(EP2C70F672C6)實現,結果顯示系統耗時為163.85μs。完全能夠保證圖像壓縮系統的實時性要求,它的值正是二維小波系數。

本文分析了提升算法的系數分布存在的特點,提出了5/3二維提升小波變換硬件實現的簡化方案,并在FPGA芯片中實現了對圖像的5/3二維提升小波變換。采用FPGA芯片實現計算量十分復雜的二維提升小波變換,可以大大提高圖像壓縮的運算速度,保證系統的實時性要求。本方法在很多領域的圖像處理中有著廣闊的應用前景。

評論