一種新型掃頻儀的設計

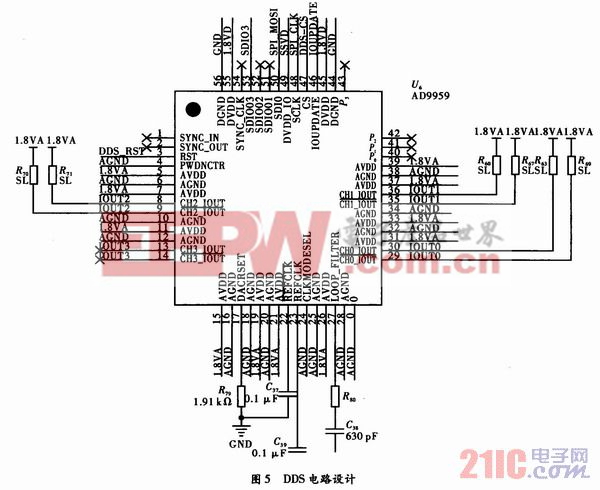

系統選用25 MHz有源晶振,通過設置寄存器中的倍頻參數,使AD9959內部的鎖相環電路倍頻產生500 MHz的系統時鐘,這一設置在DDS上電復位后完成。參考AD9959的技術手冊,設計電路如圖5所示。本文引用地址:http://cqxgywz.com/article/150589.htm

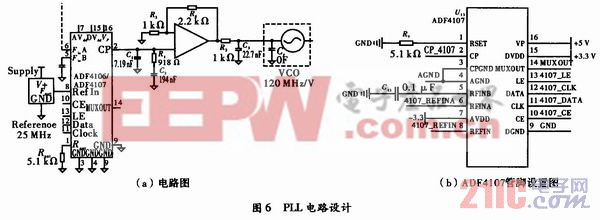

設計鎖相環電路,對DDS輸出信號完成32倍頻,頻率步進為10 Hz。后續混頻電路將該路信號作為本振信號,所以其相位噪聲和雜散指標對最終輸出信號的相位噪聲以及雜散有著直接的影響。考慮鑒相頻率范圍、相位噪聲等指標,設計選用Analog Devices公司的PLL頻率合成器ADF4107。ADF4107由低噪聲數字鑒頻鑒相器、精密電荷泵、可編程參考分頻器、可編程A和B計數器以及雙模預分頻器(P/(P+1))組成。A(6位)、日(13位)計數器與雙模預分頻器(P/(P+1))配合,可實現N分頻器(N=BP+A)。此外,14位參考分頻器(R分頻器)允許PFD輸入端的REFIN頻率為可選值。如果頻率合成器與外部環路濾波器和電壓控制振蕩器(VCO)一起使用,則可以實現完整的鎖相環。ADF4107最高鑒相頻率為104MH z,相噪基為-219 dBc/Hz,采用ADIsimPLL軟件可以方便的仿真并設計出外部鎖相環路濾波器。

4 結束語

該掃頻儀系統采用DSP+FPGA結構的設計方案。信號源是設計中的一個重要環節,決定了整個系統的指標和設計復雜度。本文在介紹PLL和DDS原理的基礎上選用DDS激勵PLL完成射頻掃頻信號源的設計,充分利用了DDS輸出頻率的靈活性和高分辨率,以及PLL電路的高輸出頻率,實現了優勢互補。

評論