可配置處理器開發原理

由于微處理器是由指令進行驅動的,因此可以通過對處理器指令執行流水線中的指令進行分析來確定在某些時間處理器的哪些部件處于運行狀態。這種分析通常需要幾十億個系統仿真時鐘周期,這樣可以讓Xtensa設計人員在處理器設計時通過增加細粒度時鐘門控來關閉那些指令執行過程中沒有執行到的處理器單元部件。進一步,如果處理器沒有執行到的TIE操作,那么Xtensa就可以對TIE擴展定義的整個系統硬件關閉時鐘。因此,Xtensa處理器可以擁有幾百個不同的門控時鐘域,這樣可以真正使得微處理器的活動功耗降到最低。

可配置處理器設計過程自動化

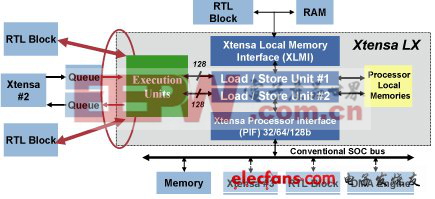

可配置Xtensa處理器能夠讓設計人員對處理器進行量身定做以滿足片上系統SOC中的特定任務。Xtensa設計流程,如圖4所示。

Xtensa 處理器生成器同時可以針對特定配置和擴展,自動生成完整而有效的軟件工具,包括編譯器、指令集仿真器、調試器、操作系統接口等軟件環境。在處理器配置信息完整的情況下,處理器生成器可以在一個小時左右生成一顆新處理器的RTL設計和軟件環境。

結論

同標準處理器一樣,可配置處理器也可以建立了一個完整的可編程的設計環境,系統軟件工具鏈可以自動產生,開發人員可以充分利用了擴展技術為應用需要來構建微處理器。

短時間內,標準處理器和可配置處理器將共存。長久看來,可配置處理器因為其可以進行架構的配置和擴展,故而能更加適應后PC時代多種應用的需求,而得到越來越廣泛的應用。

評論