ARM體系的嵌入式系統BSP的程序設計

arm公司在32位RISC的CPU開發領域不斷取得突破,其結構已經從V3發展到V6。

本文引用地址:http://cqxgywz.com/article/151077.htmBSP(Board Support Package)板級支持包介于主板硬件和操作系統之間,其功能與PC機上的BIOS相類似,主要完成硬件初始化并切換到相應的操作系統。BSP是相對于操作系統而言的,不同的操作系統對應于不同定義形式的BSP,例如VxWorks的BSP和Linux的BSP相對于某一CPU來說,盡管實現的功能一樣,可是寫法和接口定義是完全不同的。另外,仔細研究所用的芯片資料也十分重要,例如盡管arm在內核上兼容,但每家芯片都有自己的特色。所以這就要求BSP程序員對硬件、軟件和操作系統都要有一定的了解。

本文介紹基于arm體系的嵌入式應用系統初始化部分BSP的程序設計。本文引用的源碼全部是基于HMS320C7202芯片設計,并已成功運行。

1 初始化過程

盡管各種嵌入式應用系統的結構及功能差別很大,但其系統初始化部分完成的操作有很大一部分是相似的。嵌入式系統的啟動流程如圖1所示。

1.1 設置入口指針

啟動程序首先必須定義指針,而且整個應用程序只有一個入口指針。一般地,程序在編譯鏈接時將異常中斷向量表鏈接在0地址處,并且作為整個程序入口點。入口點代碼如下:

ENTRY(_start) ;開始

1.2 設置異常中斷向量表

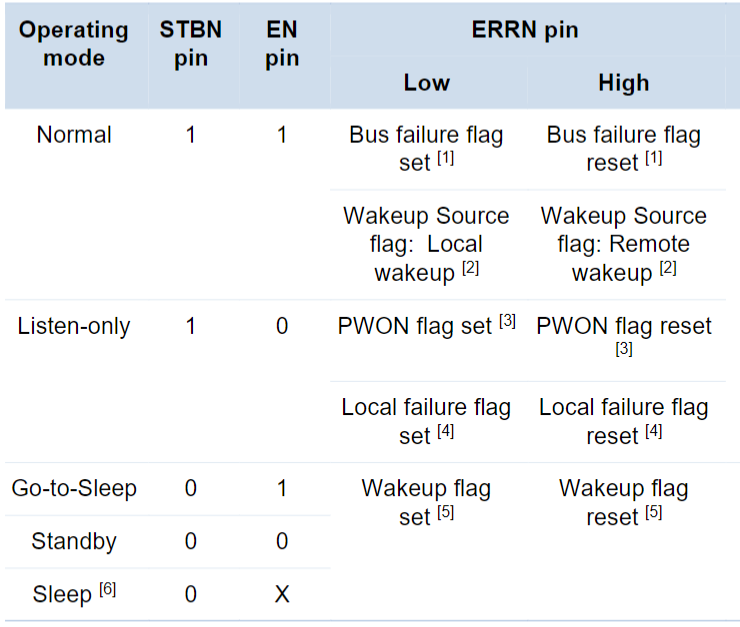

arm要求中斷向量表必須放置在從0開始、連續8×4字節的空間內。各異常中斷向量地址以及中斷的算是優先級如表1:

| 中斷向量地址 | 異常中斷類型 | 異常中斷模式 | 優先級(6最低) |

| 0x0 | 復位 | 特權模式(SVC) | 1 |

| 0x4 | 未定義中斷 | 未定義指令中止模式(Undef) | 6 |

| 0x8 | 軟件中斷(SWI) | 特權模式(SVC) | 6 |

| 0x0c | 指令預取中止 | 中止模式 | 5 |

| 0x10 | 數據訪問中止 | 中止模式 | 2 |

| 0x14 | 保留 | 未使用 | 未使用 |

| 0x18 | 外部中斷請求(IRQ) | 外部中斷(IRQ)模式 | 4 |

| 0x1c | 快速中斷請求(FIQ) | 快速中斷(FIQ)模式 | 3 |

表1 各異常中斷的中斷向量地址以及中斷的處理優先級

中斷向量地址 異常中斷類型 異常中斷模式 優先級(6最低)

0x0 復位 特權模式(SVC) 1

0x4 未定義中斷 未定義指令中止模式(Undef) 6

0x8 軟件中斷(SWI) 特權模式(SVC) 6

0x0c 指令預取中止 中止模式 5

0x10 數據訪問中止 中止模式 2

0x14 保留 未使用 未使用

0x18 外部中斷請求(IRQ) 外部中斷(IRQ)模式 4

0x1c 快速中斷請求(FIQ) 快速中斷(FIQ)模式 3

每當一個中斷發生后,ARM處理器便強制把程序計數器(PC)指針置為向量表中對應中斷類型的地址值。因為每個中斷向量僅占據放置1條arm指令的空間,所以通常放置1條跳轉指令或向程序計數器(PC)寄存器賦值的數據訪問指令,使程序跳轉到相應的異常中斷處理程序執行。如果異常中斷處理程序起始地址小于32MB,使用B跳轉指令;如果跳轉范圍大于32MB,使用LDR指令。

另外,對于各未用中斷,可使其指向一個只含返回指令的啞函數,以防止錯誤中斷引起系統的混亂。

1.3 初始化存儲系統

初始化存儲系統的編程對象是系統的存儲器控制器,一個系統可能存在多種存儲器類型的接口,不同的存儲系統的設計不盡相同。Flash和SRAM同屬于靜態存儲器類型,可以合用一個存儲器端口;而DRAM因為有動態刷新和地址線復用等特性,通常配有專用的存儲器端口。其中,SDRAM必須在初始化階段進行設置,因為大部分的程序代碼和數據都要在SDRAM中運行。

在HMS30C7202中,與SDRAM配置有關的寄存器有4個:配置寄存器、刷新定時寄存器、寫緩沖寫回寄存器和等待驅動寄存器,需要根據實際的系統設計對此分別加以正確配置。

評論