基于FPGA的數據采集板設計與實現

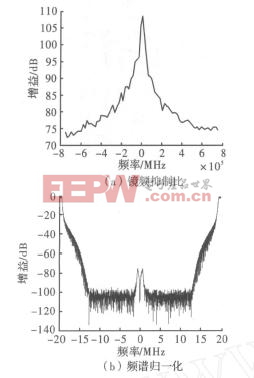

把實測數據導到Matlab進行分析, 得到鏡頻抑制比滿足系統的要求, 如圖7所示。

圖7 系統實測數據, 低通濾波法頻率歸一化后的鏡頻抑制比數據采集板實物圖, 如圖8所示。

3 結束語

文中設計的基于CPCI總線的數據采集板, 8路信號同時采集并處理, 兼備強大的數據處理能力和高實時性。整個系統實現的是數字正交采樣, 無論是中頻采樣, 還是數字下變頻, 都有一定的通用性, 在以后類似的應用中, 無需重新設計, 只需通過資源分配和算法的再實現, 足以達到預期的效果, 保證可靠性的同時也大大的縮短了研制周期。

圖8 數據采集板實物圖

實時性。整個系統實現的是數字正交采樣, 無論是中頻采樣, 還是數字下變頻, 都有一定的通用性, 在以后類似的應用中, 無需重新設計, 只需通過資源分配和算法的再實現, 足以達到預期的效果, 保證可靠性的同時也大大的縮短了研制周期。

評論