基于散列DMA的高速串口驅動設計

1 概 述

本文引用地址:http://cqxgywz.com/article/151844.htm由于串口在電報通信、工控和數據采集等領域有著廣泛的應用,絕大多數嵌入式處理器都內置了通用異步收發器(UART)。UART數據傳輸主要通過中斷或DMA的方式實現。

中斷方式是在接收到數據或需要發送數據時產生中斷,在中斷服務程序中讀寫UART的緩沖區(FIFO)實現數據傳輸。由于串口通信速率一般比較低(典型值不超過115 200 bps),大多數嵌入式系統都采用中斷方式來傳輸串口數據。然而,中斷服務程序需要占用CPU的時間,而串口速度的提升也必將導致CPU更頻繁地響應UART中斷,這勢必會造成嵌入式系統的性能下降。

DMA數據傳輸無需CPU的參與,是一種更加高效的數據傳輸方式。現有的DMA數據傳輸方案都是基于DMA塊傳輸方式(即Block DMA)。這種方式下每次傳輸完一個數據塊后產生一個DMA中斷,在高速串口通信中,頻繁的DMA中斷仍然會影響系統的性能。本文基于散列DMA(seatter DMA)的傳輸方式提出了一套完整的工業級高速串口驅動設計方案,實現了波特率高達12 Mbps的UART數據傳輸。

2 DMA數據傳輸的特點

DMA(Direct Memory Access,直接存儲器訪問),是指數據在內存與I/O設備間的直接傳輸,數據操作由DMA控制器(DMAC)完成而不需要CPU的參與,大大提高了CPU的利用率。因此,DMA是高速數據傳輸的理想方式。利用DMA進行數據傳輸時應注意以下幾點:

①DMA傳輸需要占用系統總線,在此期間CPU不能使用總線。如果外設在進行數據傳輸時不能有任何的間斷,就必須保證傳輸期間DMAC對系統總線的獨占,這可能會影響其他需要使用總線進行數據傳輸的設備。所以,系統總線在DMA傳輸期間是否可被搶占,要依據嵌入式系統的特定環境來決定。

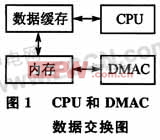

②DMA傳輸存在緩存一致性(cache coherency)問題。如圖1所示,DMAC和CPU是兩個平行的單元,CPU總是通過數據緩存來訪問內存中的數據,而DMAC則直接訪問內存。如果內存中的數據被DMAC更新,而數據緩存中的數據尚未被更新,CPU獲得的某些地址的值可能并不是內存中的真實值。為了避免這個問題,可在DMAC更新完內存數據后或CPU讀取被更新過的數據前刷新數據緩存,或是使用不被數據緩存映射的非緩存(non-cacheable)內存區域。

評論