基于雙DSP的實時圖像處理系統

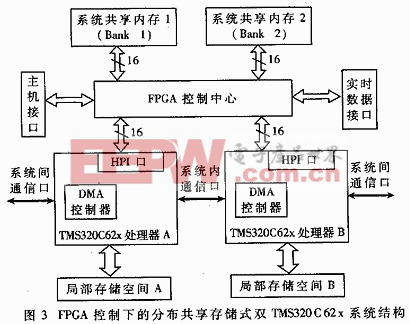

為了盡可能地獲得高性能,我們提出以兩個TMS320C62x為中央處理核心構成雙DSP處理系統,由FPGA(這里采用ALTERA的FLEX系列)實現系統互連。系統分為處理器模塊、FPGS組模塊和各總線接口模塊等,如圖2所示。其中處理器模塊包含TMS320C62x、內存空間以及相應邏輯。處理器作為最小處理單元模塊而存在,可以完成相應的處理子任務。在我們的系統中設備了兩個這樣的處理子任務。在兩個處理模塊都是在系統核心FPGA控制下運行的。而FPGA作為系統中心,負責兩個微處理器互相通信、互相協調以及它們與外界(這里通過主從總線和互連總線)的信息交換。同時,系統處理子任務可以由FPGA直接派發給處理器。靈活的FPGA體系結構設計是該系統有效性的保證。在實際應用中,可以根據系統的任務,通過配置FPGA控制兩個微處理器按流水線方式運行,也可以控制它們按MIMD方式并行處理同一輸入圖像。為了提高數據交換的效率,在FPGA控制下的數據交換中心設置了靈活的系統存儲空間。而這塊存儲空間與DSP的局部存儲空間構成了一種分布共享式的結構。然而不同于一般的分布共享式存儲結構的,我們的系統存儲空間相對獨立,不是直接掛接在各DSP的地址空間中,而是通過兩者的HPI口進行互連。從嚴格意義上講,這種結構不能算分布共享式存儲結構,而應稱之為一種松散的分布共享式存儲結構。由于并行效率要求,我們將系統存儲空間設置為兩個Bank結構,兩個Bank是獨立控制和運行的,系統的實際框圖見圖3。

由于系統的互連、各個接口以及數據通道都是通過FPGA完成,并在FPGA內部實現除一些必要邏輯之外的其它所有邏輯,因此系統的重構非常方便。這是系統設計中的最大特點。另外系統還有其它幾個優點:(1)系統可測性。由于所有的接口邏輯(包括微處理器以及板上其它接口)都由FPGA實現,并且由于系統實現主從接口邏輯,完全可通過軟件獲取系統內部運行的所有狀態。在系統調試階段,可以增加一些測試點和測試狀態字節,相當于將該信息處理子系統在一個優良有數字測試環境下運行,使得系統的可測大大提高;(2)系統可裁減性。由于FPGA的實現完全類似于軟件的編程工作,我們可以使系統設計變為軟件模塊的設計,模塊化設計方法可以使系統具有功能的可裁減性。根據不同應用環境進行不同目標的設計將擁有不同的模塊功能;(3)系統設計的方便性。由于FPGA系統的引入,我們可以改變以往的硬件設計方案和步驟,初步的硬件連線只需關注以往的硬件設計方法和步驟,初步的硬件加線只需關注系統外部特征、微處理器系統的可能控制線性,無需詳細關注更多的細節,而在系統調試時才注意邏輯接口的具體功能,并且都在FPGA上完成,這使得系統設計的周期變短。本系統已成功地應用在智能移動機器人的實時視覺導航系統的,以得了滿意的效果。

評論