基于ARM嵌入式平臺的X86譯碼SOC架構設計

1.3 各IP在系統中的功能

除了兩個處理器外,SoC中各IP核功能如下:翻譯模塊:實現將X86指令翻譯成為ARM指令的功能。

SMI:外部存儲與微處理器之間的橋梁,支持RoM作為系統的非易失性存儲介質,支持片外SRAM作為系統的外圍高速存儲。

中斷控制器:用來支持系統內部與外部的中斷控制,如中斷電平/邊沿觸發、中斷電平極性與中斷使能等。

Internal Memory:片內SRAM,大小為1 KB,但可以通過修改Verilog的描述來改變其大小。

Default Slave:用于當master訪問未定義的地址空間時,給出一個應答信號。

Retry Slave:是一個可以產生重試回應及等待命令的slave范例,若需要類似的模組,可以利用它來完成。

Watchdog:保證系統安全的監控模塊,軟件需在預定的時間內訪問相應的寄存器,否則硬件將產生內部信號自動復位。

GPIO控制器:用來支持擴展外設,拓寬SoC的使用范圍。

RemapPause:主要分成兩個處理單元,前者負責控管地址是否重新對應的機制,后者負責管理系統的省電模式。

Timer:定時器,支持捕獲、Matchout輸出、外部時鐘驅動。

2 X86到ARM二進制翻譯模塊

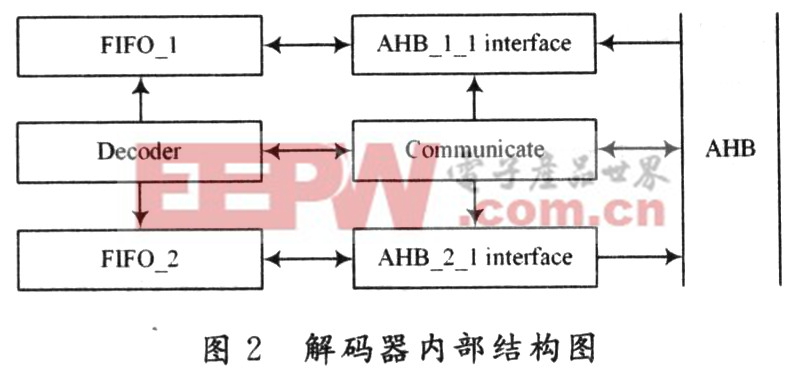

該設計使用的翻譯模塊通過編寫Verilog HDL實現,能將部分X86指令翻譯成ARM指令,實現了某些X86應用程序到ARM架構的移植。圖2為解碼器內部結構圖。

該翻譯模塊首先從ROM中取出X86指令,翻譯成ARM指令后存人RAM中,所有指令翻譯完成后,翻譯模塊產生一個終端,使處理器執行RAM中的指令。即所有指令先翻譯完成,處理器才執行,該翻譯過程屬于靜態二進制翻譯。其中Decoder是整個解碼模塊的核心,負責翻譯指令。Decoder模塊采用有限狀態機控制數據通路的方式實現.根據指令的功能和尋址方式進行狀態分類,然后輸出ARM指令。例如,把寄存器尋址的算術指令可分為一類:

ADD EAX,EBX

SUB EAX,EBX

因為這些指令的尋址方式一樣,功能近似,只是操作碼不一樣,可以歸并為一個狀態,在某一狀態內建立映射關系翻譯成為ARM指令。

考慮到AHB總線可能處于比較忙碌的狀態,對于X86指令和翻譯出的ARM指令分別設置2個FIFO。FIFO1和FIFO2各自有2個存儲器,其中一個存儲指令,另一個存儲與指令對應的地址。對FIFO進行操作會同時對指令和地址進行操作,以保持指令和地址的對應。

此外,ARM核需要向解碼模塊發送信號,通過設置Communicate模塊中的寄存器控制指令譯碼器的工作:

設置X86指令的起始地址;設置X86指令的終止地址;設置ARM指令的初始存放地址;設置ARM指令復雜指令段的初始地址;設置使指令解碼器開始工作的標志寄存器,高電平表示工作;判斷指令解碼是否結束,結束后向ARM核發送中斷;ARM核接收中斷信號后,將標志寄存器置低,翻譯模塊結束本次工作。

本文的SoC系統中沒有使用DMA對X86指令和ARM指令進行存取,而是由翻譯模塊主動進行讀和寫。因而有2個Master總線接口,通過AHB _1_1interface讀取X86指令,由AHB_2_1 interface將ARM指令寫入RAM中。Communicate模塊與總線的通信接口為Slave口,用于接收ARM核發送的4個地址,一旦接收到這4個地址,翻譯模塊中的start_flag信號置高,表示開始工作。

評論