直序擴頻的研究與FPGA實現

摘要 直接序列擴頻通信系統以強抗噪聲、低截獲性和多址通信等特點,在軍事及民用移動通信網絡中得到廣泛應用。文中對直序擴頻的FPGA實現技術進行了研究。以QuartusII為開發工具,建立了一個初步的直接序列擴頻通信系統。設計了發射模塊和接收模塊,發射模塊包括PN碼產生器、擴頻調制器、接收模塊包括匹配濾波器和解擴器;給出了上述模塊的實現電路及仿真結果。

關鍵詞 直序擴頻;FPGA;PN碼;匹配濾波器

擴頻通信是現代通信系統中的一種獨特的通信方式,其擁有較強的抗干擾、抗多徑性能以及頻譜利用率高、多址通信等諸多優點。直接序列擴頻被許多現存的和未來的蜂窩通信系統采用,并廣泛應用在軍事通信網絡與系統中。

隨著微電子制造工藝的發展,可編程邏輯器件取得了長足的進步。可以完成超大規模的復雜組合邏輯與時序邏輯的現場可編程邏輯器件(FPGA),在電子系統的設計中得到越來越廣泛的應用。

以Quartus II軟件為開發工具,利用FPGA實現了一個基帶直接序列擴頻通信系統,其包括發送模塊和接收模塊兩部分。

1 直序擴頻通信系統的基本原理

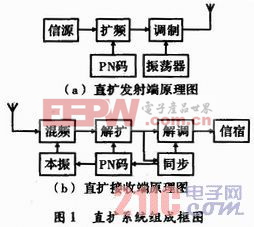

直接序列擴展頻譜系統(Direct Sequece Spread Spectrum Communication Systems,DS-SS),簡稱直擴系統,是用待傳輸的信息信號與高速率的偽隨機碼波形相乘,去調制射頻信號的某個參量,來擴展傳輸信號的帶寬。原理如圖1所示。

在發信機端,待傳輸的數據信號與偽隨機碼波形相乘形成的復合碼對載波進行調制,然后由天線發射。在收信機端,要產生一個和發信機中的偽隨機碼同步的本地參考偽隨機碼,對接收信號進行解擴。解擴后的信號送到解調器解調,恢復出傳送的信息。

2 直序擴頻通信系統發送模塊的設計與實現

發射子系統主要包括信息碼的輸入模塊、擴頻偽隨機碼的產生模塊及擴頻模塊。

2.1 信息碼輸入模塊

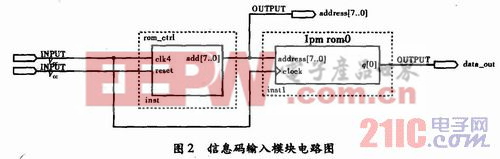

該模塊提供系統仿真及調試用的輸入數據源,數據固化在ROM中。設置為200字長、1位寬。設計ROM的地址控制模塊,以給定的時鐘驅動一個計數器來循環產生地址信息,使得ROM中存儲的待發射信息循環不斷的輸出。

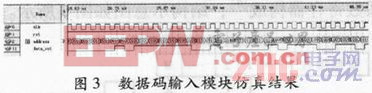

利用Verilog語言設計地址控制模塊,利用QuartusⅡ提供的LPM定制ROM模塊,用原理圖設計生成頂層實體,可得如圖2所示的電路及圖3所示仿真結果。

從結果可以看出,在時鐘控制下,地址輸入端循環產生地址信息使ROM中的數據循環輸出。

評論