TMS320TCI6612/14 助力小型蜂窩基站實現高性能

TCI6612 與 TCI6614 具有多個專用高性能嵌入式協處理器,可執行無線基站應用常見的密集型信號處理功能。這些協處理器具體包括:4 個增強型維特比解碼器協處理器(VCP2_A、VCP2_B、VCP2_C 以及 VCP2_D)、3 個第三代渦輪解碼器協處理器(TCP3d_A、TCP3d_B 以及 TCP3d_C)、渦輪編碼器協處理器 (TCP3e)、3 個高速傅里葉變換協處理器(FFTC_A、FFTC_B 和 FFTC_C)以及 1 個位速率協處理器。將其結合在一起,可顯著加速通道編碼/解碼運算。SoC 中另外還包含有 4 個緊密耦合的耙式/搜索加速器 (RSA),可用來實現協助芯片速率處理的碼分多訪問 (CDMA)。

提供完整的多核優勢

TCI6612 和 TCI6614 SoC 建立在 TI KeyStone 多核架構基礎上。KeyStone 是第一款可實現完整多核優勢的架構,可對所有處理內核、外設、協處理器以及 I/O 實現順暢訪問。并可實現完整多核優勢的創新技術,其包括 Multicore Navigator、TeraNet、多內核共享存儲器控制器 (MSMC) 以及 HyperLink 等。

BCP 架構

Multicore Navigator — TI Multicore Navigator 是一款基于數據包的創新型管理器,可對 SoC 上各個子系統間的連接進行控制與抽象。Multicore Navigator 提供支持通信、數據傳輸以及任務管理的統一接口,可實現支持更少中斷與更簡單軟件的更高系統性能,堪稱“放棄即忘”的典范。Multicore Navigator 的優勢包括:

l 動態資源/負載共享;

l 可取消與子系統間通信有關的 CPU 開銷/延遲;

l 基于硬件的任務優先排序;

l 動態負載平衡;

l 對所有 IP 模塊(軟件、I/O 以及加速器)采用統一的通信方法。

TeraNet — 是一種分層交換結構,結合在一起可在 SoC 內部為數據傳輸提供大于 2 兆兆位的帶寬。這樣事實上可以保證內核或協處理器不會缺乏數據,可實現應有的處理性能。由于該交換結構是分層的,并非扁平結構,因此閑置狀態下的整體功耗非常低,可以支持最小化系統時延。而且低時延正是新一代基站的重要要求。

多核共享存儲器控制器 (MSMC) — TI TCI6612 和 TCI6614 采用獨特的存儲器架構,可提高性能。TI 多核共享存儲器控制器 (MSMC) 可讓內核直接訪問共享存儲器,無需占用任何 TeraNet 帶寬。MSMC 可在內核與其它 IP 模塊之間判斷對共享存儲器的訪問,可消除存儲器爭用。代碼共享存儲器訪問可為代碼及數據提供高效率的預讀取機制,其時延非常接近本地 L2 訪問的時延水平。

TI TCI6612/TCI6614 的 DDR3 外部存儲接口 (EMIF) 是一個支持 8GB 可尋址存儲空間的1,600 MHz 64 位總線。該 DDR3 EMIF 直接與 MSMC 連接,不但可降低與外部存儲器存取有關的時延,而且還可為運算大量數據的更大型應用提供更快的速度與支持,從而可滿足高級 3G 和 4G 基站的應用需求。

HyperLink — HyperLink 具有 4 個通道,每通道速率達 12.5Gbaud,是一種專用的高速互聯技術,其可通過低級協議與其它 KeyStone 設備實現高速通信與連接,能夠為 OEM 廠商提供支持可擴展解決方案的無縫路徑。TCI6612 和 TCI6614 的 HyperLink 與Multicore Navigator 配合,可透明地向多個設備派發任務,讓其執行猶如在本地資源上運行一樣。

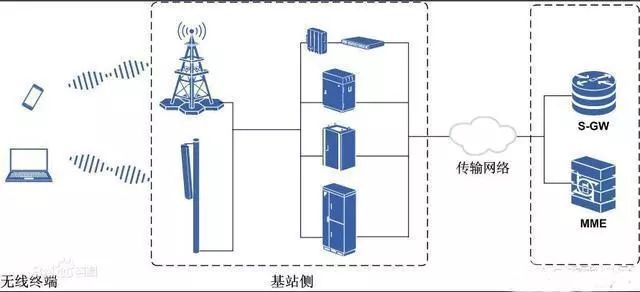

TCI6612/TCI6614 可作為 2層2和傳輸處理引擎

TCI6612 和 TCI6614 將無可匹敵的 PHY 處理功能與專用協處理器進行完美整合,支持 層2及傳輸層處理。這使設計人員無需單獨網絡處理器,便可創建基站,從而可在保證性能的同時降低電路板復雜性。

該網絡協處理器能夠在傳輸網絡層以及更深的無線電網絡的 2 層實現快速通道處理。在 SoC 的網絡協處理器中,數據包加速器與安全加速器可執行全面加速的自動包對包處理。它們可充分利用 Multicore Navigator,使用零復制方法優化各層的數據處理。該網絡協處理器可全面支持分類與排序、多核可訪問存儲、存儲器管理、分段與裝配以及在多個內核與器件中進行交付等多項功能。

由于采用了快速通道與零復制處理技術,因此 層2數據層及傳輸層的開銷可降低 10 至 15 倍。

最低功耗,卓越性能

TI 在為市場提供最低功耗的無線基站 SoC 方面擁有豐富的經驗。它在每一個無線基站半導體器件中整合了其工藝技術、SmartReflexTM 技術,并前瞻性地使用了電源管理技術(例如自適應電壓調節),可將工作電源降至最低,從而可實現其極限低功耗。TI TCI6612 和 TCI6614 的最新技術為小型蜂窩基站帶來了業界最低水平的 SoC 功耗,每 Mbps 數據傳輸僅為 26 mW。

完善的工具,全面的支持

TI 可提供一整套與 TCI6612 和 TCI6614 配套的、基于 Eclipse 的業界最佳開發及調試工具,其中包括新型 C 語言編譯器、簡化編程與調度的匯編優化器、用于查看源代碼執行情況的 Windows 調試器界面等。TI 編譯器可生成高效率代碼,能夠一次性執行通過,很少需要優化。TI 調試工具可幫助開發人員實現問題的可視化,并快速解決這些問題,因此開發人員可在節約開發資源的同時更快地將產品投入應用。此外,TI 還將提供評估板 (EVM) 幫助客戶快速進行原型設計。所有這些工具還集成 ARM RSIC 處理器,可幫助設計人員迅速高效地為 SoC 的所有子系統開發代碼。

評論