基于DDS的勵磁恒流源設計

摘要 針對某型磁性材料性能測試儀激勵恒流源的具體要求,采用了基于直接數字頻率合成技術的信號發生器設計方法,重點研究了由FPGA設計DDS信號發生器的系統設計原理、硬件構成,以及在Quartus開發環境下。采用硬件描述語言Verilog HDL完成信號發生器的累加器、波形存儲表、幅度控制及濾波控制功能,并使用Modelsim進行仿真分析。實驗結果表明,該信號發生器能較好地產生所需激勵信號,符合設計技術指標。

關鍵詞 直接數字頻率合成;現場可編程門陣列;信號源;磁性測量

隨著信息技術的發展,磁性材料廣泛運用于通信、電力、信息、交通等領域中。磁滯回線是磁性材料中重要的磁性參數之一,是鐵磁材料的本質特征。通常運用于與磁性材料有關的計算和研究中,對工業生產和科學研究具有重要的指導意義。材料的磁滯回線通過B-H測試儀可以測量得到,測試儀以電磁感應原理為基礎,通過勵磁電源對軟磁材料樣品的初級繞組加一定頻率和幅度的電流,次級繞組兩端將會產生感應電動勢,對初級勵磁電流和次級感應電動勢實施同步實時采樣。根據安培環路定理和電磁感應定理計算磁場強度H和磁感應強度B,進而可以計算動態回線,動態磁化曲線、鐵損、動態磁導率等參數。勵磁信號源主要包括正弦信號發生電路和功放電路兩部分。目前勵磁電源信號發生部分通常采用直接頻率合成技術,主要功能電路由壓控振蕩器(VCO)、倍頻器、分頻器、混頻器和濾波器等構成,整個系統采用開環控制,即輸入設定值→頻率合成→功率放大→輸出勵磁電流。這種結構給勵磁電源帶來以下不足:(1)由于采用外部壓控振蕩器,勵磁信號的頻率范圍受到限制,一般約為50 kHz。(2)系統使用開環控制,系統精度依賴于各組件的精度和穩定性,使得勵磁電流的幅度精度和穩定性較差,儀器抗干擾性不強。(3)采用直接頻率合成技術,系統中有大量模擬電路,導致系統體積大、重量大、耗電高、可靠性差。

為此,文中提出一種基于FPGA的DDS信號發生器。信號發生電路采用直接數字頻率合成技術,即DDS(Direct Digital Frequency Synth-esis)。它是以全數字技術,從相位概念出發,直接合成所需波形的一種新的頻率合成技術。是將先進的數字處理技術和方法引入信號合成領域,把一系列數字量形式的信號通過數/模轉換器轉換成模擬信號,在時域中進行頻率合成。直接數字頻率合成器的主要優點是:輸出信號頻率相對帶寬較寬;頻率分辨力好、轉換時間快;頻率變化時相位保持連續;集成度高,體積小,控制方便等。整個信號源系統采用數字閉環控制,通過對勵磁電流瞬時值經PID閉環控制,使得勵磁電流可瞬時跟蹤給定幅值,加快系統動態響應,提高非線性負載適應力,其較傳統的信號源能更好地滿足磁性測試設備的需求。

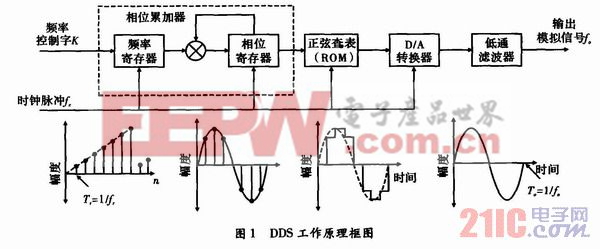

1 DDS的工作原理

DDS的工作原理如圖1所示。主要有以下基本部件:相位累加器;相位-幅度變換器,即正弦查表ROM;D/A轉換器和適當的濾波器等濾波器。相位累加器是DDS系統的核心是相位累加器,它由一個加法器和一個相位寄存器組成,相位累加器在參考時鐘的作用下,按頻率控制字為步長不斷累積,累加結果產生遞增的傳遞給正弦查表ROM。正弦查詢表中存儲了一個周期正弦波在各相位點對應數字幅度信息。由于相位累加器的輸出連接在波形存儲器(ROM)的地址線上,因此其輸出的改變就相當于進行查表。這樣就可把存儲在波形存儲器內的波形抽樣值經查找表查出,然后送至D/A轉換器,經D/A轉換器產生一系列以時鐘脈沖為抽樣速率的電壓階躍。濾波器則進一步平滑D/A轉換器輸出的近似正弦波的鋸齒階梯波,同時衰減不必要的雜散信號,使輸出為要求的光滑波形。

由于相位累加器字長的限制,相位累加器累加到一定值后,其輸出將會溢出,這樣波形存儲器的地址就會循環一次,即意味著輸出波形循環一周。故當頻率字取不同值,就可以改變相位累加器的溢出時間,從而在時鐘頻率不變的條件下改變輸出頻率。

設頻率控制字為K,系統參考時鐘為fc,相位累加器位數為N,輸出頻率為fo,則可以得到輸入與輸出的關系為

![]()

當K=1時,可以得到DDS的頻率分辨率

![]()

評論