基于千兆以太網的高速數據傳輸系統設計

2.3 系統實現

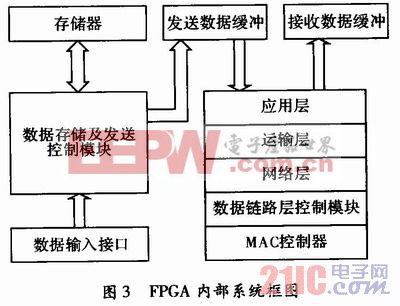

千兆以太網由物理層、數據鏈路層、網絡層、運輸層和應用層組成。在FPGA內部實現MAC層以及MAC層以上的部分TCP/IP協議,其中包括ARP協議,IP協議,UDP協議以及部分ICMP協議。物理層使用DP83865芯片。FPGA內部系統框圖如圖3所示。本文引用地址:http://cqxgywz.com/article/156459.htm

MAC控制器上層的協議在FPGA內部用硬件描述語言實現,這些協議將與MAC核共同組成網絡控制系統,各部分協議之間密切配合,共同完成網絡數據收發的功能。協議系統的時鐘速率設定為125 MHz,可以最大程度地發揮MAC核的作用,使千兆以太網的數據吞吐率達到最大。

系統中關鍵的技術問題在于協議的效率問題。在調試初期,先以百兆速度運行,由于系統時鐘為25 MHz,相對較低,沒有出現程序因效率低下而導致系統不穩定的情況。當在原有基礎上改為千兆以太網時,系統出現不穩定地情況,所發送的數據幀不能穩定地發送至上位機,有丟失數據幀的情況。

于是對協議部分進行優化,以提高其運行效率。在編寫程序時,良好的代碼風格尤為重要。時序電路中最重要的是狀態機,所以狀態機的性能在一定程度上決定了整個程序的性能。協議中狀態轉移比較復雜,對狀態進行合并、減少狀態數量之后,程序效率明顯提高。此外,由于需要處理大批量的數據,而且數據將流經每一層協議,因而各層協議之間使用完全流水結構,銜接緊密,實時性更高,而且不必為每一

層開辟緩沖區,節省了資源。

2.4 上位機控制

使用Visual C++編寫上位機程序,上位機通過網絡向FPGA發送相關命令,FPGA接收到命令后進行相應操作,并將數據通過千兆以太網發送至計算機,由上位機程序對接收到的數據進行存儲。上位機程序在MFC環境下使用WinSock編程實現,使用面向無連接的數據報套接字,即采用UDP協議,無需建立連接。為提高系統效率,在程序中使用多線程技術,一個線程負責接收數據,一個線程負責存儲數據,可以有效提高程序運行效率。

2.5 測試結果

在系統中,將存儲在電路板上Flash中的數據通過千兆以太網傳輸至計算機,使用UDP協議,每次傳輸1 024 Byte。經測試,此千兆以太網性能穩定,數據吞吐率高。圖4所示是由SignalTap II采樣得到的由FPGA輸出的UDP波形,采樣時鐘為250 MHz。

在圖4中,rx_clk為125 MHz時鐘,gm_tx_d是由MAC發送至物理層芯片的數據幀。由圖可見,MAC軟核每個時鐘周期發送8 bit數據,則此千兆以太網帶寬為1 000 Mb·s-1。千兆以太網額外開銷小,大約占用FPGA資源的7%,為系統留下了充足的設計空間。對千兆以太網進行測試時,每次發送數十萬數據幀至上位機,當檢測到錯誤幀或數據幀丟失時立即停止發送,在所進行的一系列測試中,沒有出現中途停止發送的情況,說明沒有數據幀丟失或在傳輸中出錯,系統工作穩定。

數據傳輸至計算機后由上位機程序接收并存儲,由于上位機程序效率偏低,千兆以太網傳輸速率受到限制。如果進一步優化上位機程序,可以提高千兆以太網帶寬利用率。若兩個電路系統使用千兆以太網互連,因為都是純硬件電路,運行效率較高,可以發揮千兆以太網高帶寬的特性。

3 結束語

設計中使用三速以太網軟核,并對源程序進行了一系列優化,代碼效率較高,系統工作穩定,資源利用率較高,數據吞吐率最高可達1 000 Mb·s-1。千兆以太網成本低,可以在多種平臺下應用,為高速數據傳輸提供了方便的途徑。

tcp/ip相關文章:tcp/ip是什么

評論