基本觸發器的邏輯結構和工作原理分析介紹

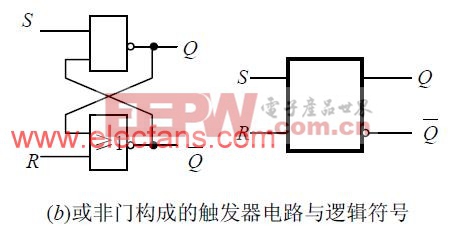

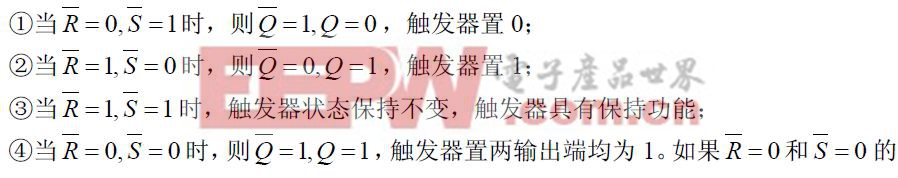

基本觸發器的邏輯結構如圖13-1所示。它可由兩個與非門交叉耦合構成,圖13-1(a)是其邏輯電路圖和邏輯符號,也可以由兩個或非門交叉耦合構成,如圖13-1(b)所示。

本文引用地址:http://cqxgywz.com/article/160942.htm

現在以兩個與非門組成的基本觸發器為例分析其工作原理。

在圖13-1(a)中,A和B是兩個與非門,它可以是TTL門,也可以是CMOS門。Q和 是觸發器的兩個輸出端。當Q=0,

是觸發器的兩個輸出端。當Q=0, =1時,稱觸發器狀態為0,當Q=1,

=1時,稱觸發器狀態為0,當Q=1, =Q時,稱觸發器狀態為1。觸發器有兩個輸入端SR、,字母上的非號表示低電平或負脈沖有效(在邏輯符號中用小圓圈表示)。根據與非邏輯關系可寫出觸發器輸出端的邏輯表達式:

=Q時,稱觸發器狀態為1。觸發器有兩個輸入端SR、,字母上的非號表示低電平或負脈沖有效(在邏輯符號中用小圓圈表示)。根據與非邏輯關系可寫出觸發器輸出端的邏輯表達式:

根據以上兩式,可得如下結論:

持續時間相同,并且同時發生由0變到1,則兩個與非門輸出都要由1向0轉換,這就出現了所謂的競爭現象。假若與非門A的延遲時間小于B門的延遲時間,則觸發器將最終穩定在Q=0, =1的狀態。因此,在

=1的狀態。因此,在 而且又都同時變為1時,電路的競爭使得最終穩定狀態不能確定。這種狀態應盡可能避免。但假若

而且又都同時變為1時,電路的競爭使得最終穩定狀態不能確定。這種狀態應盡可能避免。但假若 后,

后, 和

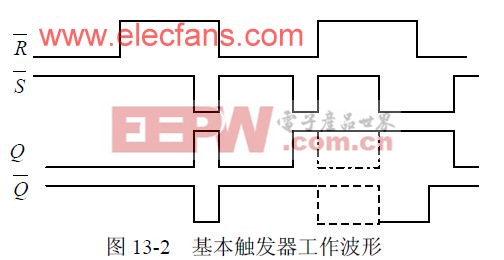

和 不是同時恢復為1,那么最后穩定狀態的新狀態仍按上述①或②的情況確定,即觸發器或被置0或被置1。圖13-2所示為基本觸發器的工作波形。圖中虛線部分表示不確定。

不是同時恢復為1,那么最后穩定狀態的新狀態仍按上述①或②的情況確定,即觸發器或被置0或被置1。圖13-2所示為基本觸發器的工作波形。圖中虛線部分表示不確定。

由上述分析可見,兩個與非門交叉耦合構成的基本觸發器具有置0、置1及保持功能。通常稱 為置1端,因為

為置1端,因為 =0時被置1,所以是低電平有效。

=0時被置1,所以是低電平有效。 為置0端,因為

為置0端,因為 =0時置0,所以也是低電平有效。基本觸發器又稱置0置1觸發器,或稱為RS觸發器。

=0時置0,所以也是低電平有效。基本觸發器又稱置0置1觸發器,或稱為RS觸發器。

需要強調的是,當 =0,

=0, =1,觸發器置1后,如果

=1,觸發器置1后,如果 由0恢復至1,即

由0恢復至1,即 =1,

=1, =1,觸發器保持在1狀態,即Q=1。同理,當

=1,觸發器保持在1狀態,即Q=1。同理,當 =1,

=1, =0時,觸發器置0后,

=0時,觸發器置0后, 由0恢復至1,即

由0恢復至1,即 =1,

=1, =1時,觸發器保持在0狀態,即Q=0。這一保持功能和前面介紹的組合電路是完全不同的,因為在組合電路中,如果輸入信號確定后,將只有唯一的一種輸出。

=1時,觸發器保持在0狀態,即Q=0。這一保持功能和前面介紹的組合電路是完全不同的,因為在組合電路中,如果輸入信號確定后,將只有唯一的一種輸出。

評論