高可靠性微控制器設計研究

3.2內部 RAM本文引用地址:http://cqxgywz.com/article/163360.htm

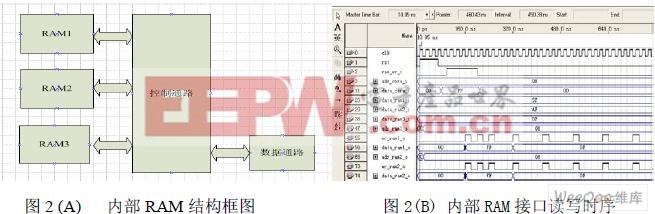

該 IP核可支持 128字節內部RAM.由 2.3分析,方案采用 TMR方式對內部 RAM進行處理,選用 3個相同的 128字節的 RAM作為冗余的存儲器,由 mc8051_ram_fsm與 mc8051_ram_dataflow兩個模塊組成了內部 RAM的數據通路,其中前者完成寫優先的讀寫狀態控制,后者完成數據流向控制。數據通路負責完成數據校驗。控制通路與數據通路組成內部 RAM接口邏輯。經過仿真后內部 RAM接口結構框圖及讀寫時序如下:

圖 2(B)可看出:寫數據時,數據輸入后第二個周期被寫入RAM;讀數據時,讀指令被檢測到后的第 5個周期經校驗后的正確數據被輸出并且被回寫給RAM。在接入工程應用時需將外部時鐘進行 6倍頻以配合 cpu讀寫時序。

3.3 外部 RAM

外部 RAM最大可以支持64K,同樣由 2.3分析,方案選取能糾 1位錯檢 2位錯的擴展漢明碼進行 EDAC處理。其中,數據處理單元完成數據的編碼,解碼,地址鎖存及數據輸出功能。讀寫狀態機 FSM完成外部 RAM的讀寫狀態控制,同樣,為配合 ram的 IP軟核時序,我們將 FSM設計為寫優先。仿真后的 EDAC結構框圖及讀寫時序如下:

需要指明的時上圖仿真時外部時鐘為 10Mhz,經過 altera公司 alt_pll進行了 6倍頻及相位調整,前一個寫指令未被執行的原因是 PLL需要 2到 3個時鐘周期的調整穩定頻率輸出。 EDAC模塊的讀寫時序與內部 RAM相似,寫數據時第 2個時鐘周期經過處理后的 8位原數據以及 4位校驗數據一同被寫進 RAM,讀數據時,讀出的 12位數據經過解碼糾正后在第 5個時鐘周期輸出 8位數據并將糾正后的 12位數據回寫進 RAM,以防止 SEE的積累。由時序圖可知以上設計完全符合設計要求。

3.4全系統仿真

在完成上述幾個方面的 IP定修改之后,對 mc8051的頂層系統進行了 modelsim的綜合前仿真,仿真部分結果如下:

仿真時將 ROM的初始化文件設置為 mc8051文檔中的 tc1.hex,方便與原 IP核進行對照。為在 modelsim仿真前,我們已將 altera的 altera_mf庫加入到 modelsim庫文件中。在進行功能仿真的時候調用了其中的 alt_pll來進行時鐘處理。在使用該 IP核時可以根據具體采用的器件來完成倍頻的功能。以上時序完全正確,說明修改后的 IP核與原 IP核功能上等同。

4結論

本文在oreganosystems公司提供的開源mc8051IP軟核的基礎上根據高可靠性航天電子設計的方法修改了部分模塊,實踐證明修改后的功能與原 mc8051IP 核完全相同,達到設計目的。可以根據需要將 IP核綜合后生成的網表文件下載進現場可編程邏輯器件( FPGA)或者進行流片設計成 ASIC,具備航天使用價值。本文創新點:本文根據在研航天項目需要,定制了一種可適應航天工作環境的微控制器 IP核。采用常用的容錯技術對普通商用 IP核進行了加固。該 IP核的成功改造,可以一定程度上減輕我國軍品級芯片對國外的依賴,提高了效率,為后續的研究積累了寶貴經驗。

評論