基于AMBA總線的智能卡控制器設計

塊傳輸(如圖5所示)的接收過程和字符傳輸類似,按照起始位、8 b數據位的狀態機接收數據。一個字節接收完畢后返回IDLE,當沒有發送任務時就進入下一次起始位等待。一個字節數據發送完畢后有若干個ETU的保護時間,然后進入Prepare狀態準備發送下一個字節數據。當所有數據發送完畢后,系統維持一個塊保護時間BGT(Block Guard Time),然后進入IDLE等待新任務。

3.3 讀寫數據緩沖器模塊

由于APB總線上連接多個功能模塊,如USB,UART等都需要占用總線進行數據傳輸,智能卡控制器只能通過發出總線請求在有限時間占有總線。這使得在進行智能卡讀寫操作時會申請不到總線從而來不及存儲已收到的數據或者來不及獲取新的發送數據,增加讀寫數據緩沖器實現數據暫存可以很好地解決這個問題。緩沖器采用寬度為8位,深度為16的同步FIFO。該FIFO通過在最高位額外設置1 b來判斷空/滿標志位。當讀寫指針的8 b數據位和1 b最高位都相同時,FIFO為空。當讀寫指針的8 b數據位相同并且1 b最高位相反時,FIFO為滿。根據FIFO的空滿狀態來請求或停止新的數據。

3.4 APB總線接口模塊

ARM內核通過APB總線讀寫智能卡控制器,完成了對寄存器的設置、中斷狀態的讀取以及收發數據的讀寫,讀寫時序需要符合AMBA APB總線協議。

系統通過總線接口模塊設置了控制器工作頻率,傳輸方式、編碼方式、時鐘轉換因子、波特率調整因子。當解析出智能卡為異步半雙工字符傳輸模式時,設置字符發送完畢后的保護時間和最大等待時間。當解析出智能卡為異步半雙工塊傳輸模式時,設置塊之問保護時間,最大等待之間,以及塊內字符間的最大等待時間。系統按照上述設置工作。

系統在設定的參數下完成對接收FIFO的讀取和對發送FIFO的寫人,并且發出讀寫使能信號控制FIFO讀寫。

在收發控制模塊產生中斷后,對中斷狀態寄存器設置并交由軟件處理。

4 仿真結果及FPGA驗證

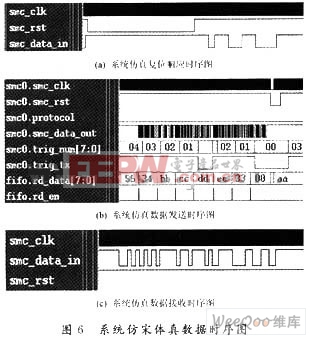

智能卡控制器采用RTL級的Verilog實現,在系統仿真過程中編寫智能卡仿真模型。使用Synopsys公司VCS對控制器進行功能仿真和驗證。對智能卡的數據收發波形如圖6所示。

從仿真結果可以看出,智能卡控制器符合ISO7816-3協議,可以對智能卡進行復位及讀寫操作。

在FPGA驗證中,采用Altera公司的StratixⅡ芯片。將智能卡控制器、AMBA總線等模塊的RTL代碼燒錄到ARM開發板的FPGA中,并且將外接一塊帶有智能卡插槽的擴展板與ARM開發板連接。使用ARM的調試軟件ARMulator對控制器進行功能測試。測試結果表明該控制器可以成功完成對智能卡的復位和數據讀寫操作。

5 結 語

根據上述VCS仿真和FPGA驗證的結果,說明該智能卡控制器已經達到功能要求,實現了ISO/IEC7816-3傳輸協議。利用Design Compiler對該模塊進行綜合并編寫腳本對芯片的面積和時序進行優化,最終邏輯單元為1 368 cells,符合設計目標,實現了對智能卡的數據復位及收發操作。

評論