基于DSP Builder的帶寬自適應全數字鎖相環的設計與實現

本文引用地址:http://cqxgywz.com/article/166449.htm

本文引用地址:http://cqxgywz.com/article/166449.htm

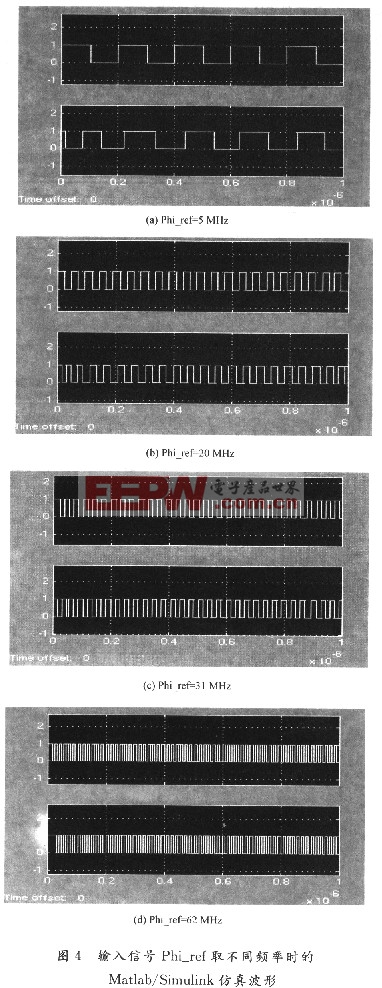

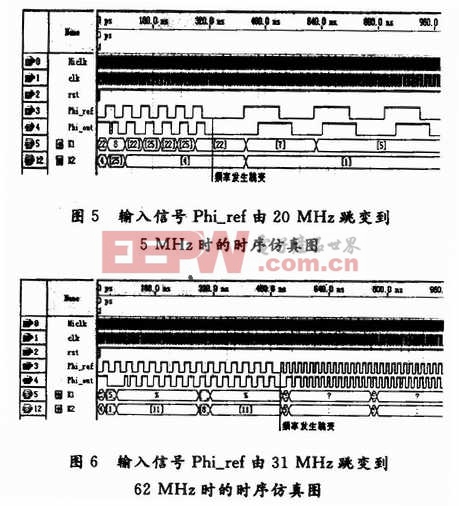

使用DSP Builder庫中的Signal Compiler模塊將圖3建立的全數字鎖相環模型轉化為VHDL語言代碼。該設計通過QuartusⅡ軟件完成帶寬自適應全數字鎖相環的整體時序仿真。圖5為輸入信號Phi_ref由20 MHz跳變到5 MHz時的時序仿真圖;圖6為輸入信號Phi_ref由31 MHz跳變到62 MHz時的時序仿真圖。通過對所設計的全數字鎖相環的Matlab/Simu-link仿真和QuartusⅡ時序仿真可以看出:該系統能夠實現鎖頻的功能;同時該系統具有自適應的特性,在輸入信號很大變化范圍內都具有良好的性能;最后該系統對頻率發生階躍跳變的輸入信號亦具有很好的跟蹤性能。

3.2 FPGA實現及硬件測試

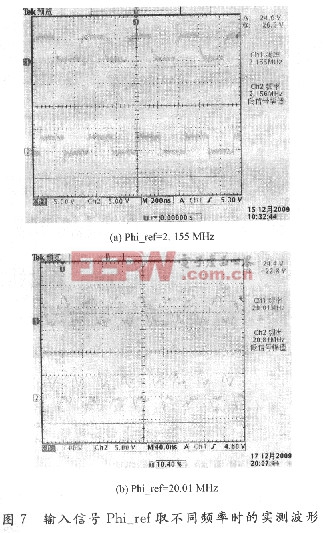

由于Signal Compiler模塊可以自動地將DSPbuilder建立的模型文件轉化為QuartusⅡ環境下的工程文件,因此,該設計在完成軟件仿真后結合FPGA試驗箱,在生成的工程下進行引腳的鎖定、編譯適配下載到FPGA芯片,實現所設計的帶寬自適應全數字鎖相環,并完成硬件測試。在硬件測試中需要用到信號發生器和示波器,信號發生器用來產生鎖相環的輸入測試信號,示波器用來觀測鎖相環的輸入/輸出波形。圖7為輸入信號Phi_ref取不同頻率時的實測波形。

以上的軟件仿真與硬件測試都表明,設計的帶寬自適應全數字鎖相環系統能過實現鎖頻的功能,設計是成功可行的。

4 結語

本文使用DSP Builder建立系統模型完成全數字鎖相環設計,理論分析和仿真結果基本一致。從以上設計過程可以看出:基于DSP Buil-der完成全數字鎖相環設計的方法,使得設計者可以利用Simulink快捷靈活的建模仿真功能和Matlab強大的數據分析能力進行FPGA系統級的建模仿真,并使得設計者從編寫VHDL或者Verilog HDL等代碼語言的繁瑣工作中解放出來,而專注于在Matlab/Simulink下搭建系統模型的工作上,縮短了設計周期,提高了設計的靈活性。

評論