基于ADSP-BF5619處理的H.264視頻編碼器設計

0 引言

H.264/AVC是ITU-TVCEG和ISO/IEC MPEG聯合制定的最新視頻編碼國際標準,是目前圖像通信研究領域的熱點問題之一。H.264的視頻編碼層(VCL)采用了許多新技術,因而使得編碼性能大幅度提高。與以往的視頻編解碼標準相比,在相同的碼率下,H.264具有更佳的圖像質量,這使得H.264在無線通信和網絡傳輸等低碼率視頻應用領域得到了更為廣泛的應用。但這是以復雜度的成本增加為代價的,故使H.264在實時視頻編碼及傳輸應用中面臨巨大的挑戰。而用高性能數字信號處理器(DSP)來實現H.264實時編碼器是一種快速有效的方法,有助于H.264視頻標準的迅速推廣和應用。ADSP-BF561處理器性能卓越,具有600 MHz的主頻,且集成了一套通用的數字圖像處理外圍設備接口,從而為多媒體和圖像應用創建了一個完美的系統級片上解決方案。本文針對低碼率視頻傳輸的需要,研究并實現基于H.264標準的視頻編碼系統,同時探討H.264軟件編碼器在DSP上的實現及優化方法。

1 H.264編碼算法及ADSP-BF561簡介

在實際開發過程中,針對H.264的算法特點和ADSP-BF561雙核處理器的結構特性,本文做了大量優化工作,從而在保證編碼精度的同時,大幅度提高了編碼速度。下面簡要介紹H.264視頻編碼算法和ADSP-BF561雙核處理器系統。

1.1 H.264編碼算法

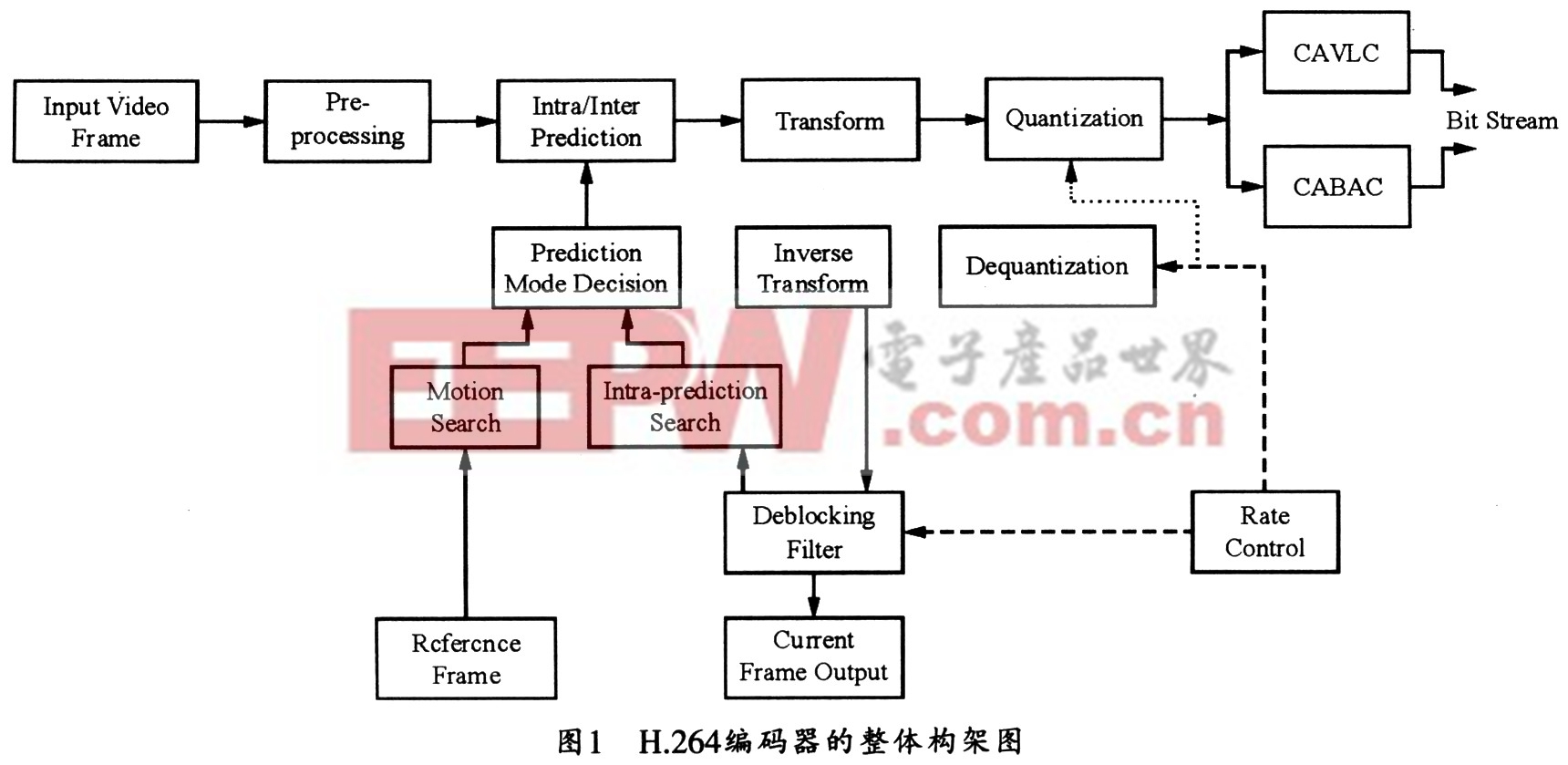

H.264是ISO和ITU聯合制定的新一代視頻編碼標準,具有很高的壓縮比和很好的魯棒性。其整體框架如圖1所示。

在繼承了原有視頻編碼標準的基礎上,H.264作了多方面的改進,包括引入4×4子塊和16x16子塊共9種模式的幀內預測。幀內模式的引入是為了與變換編碼一起用于消除空間上的冗余,進而大大提高編碼效率。在幀間模式中,H.264可支持多尺寸的運動估計和補償。其幀間預測時塊的大小不是固定的8x8,而是可以從4×4到16x16,并且包括長寬不等的塊(共7種類型),同時支持多參考幀,故可大大提高預測性能。此外,H.264還采用整數DCT變換來降低計算量,同時采用自適應算術編碼來提高編碼效率,并可利用濾波器消除低比特量化帶來的塊效應等。事實上,H.264的效率比現有的編碼技術可提高50%。

1.2 ADSP-BF561芯片結構

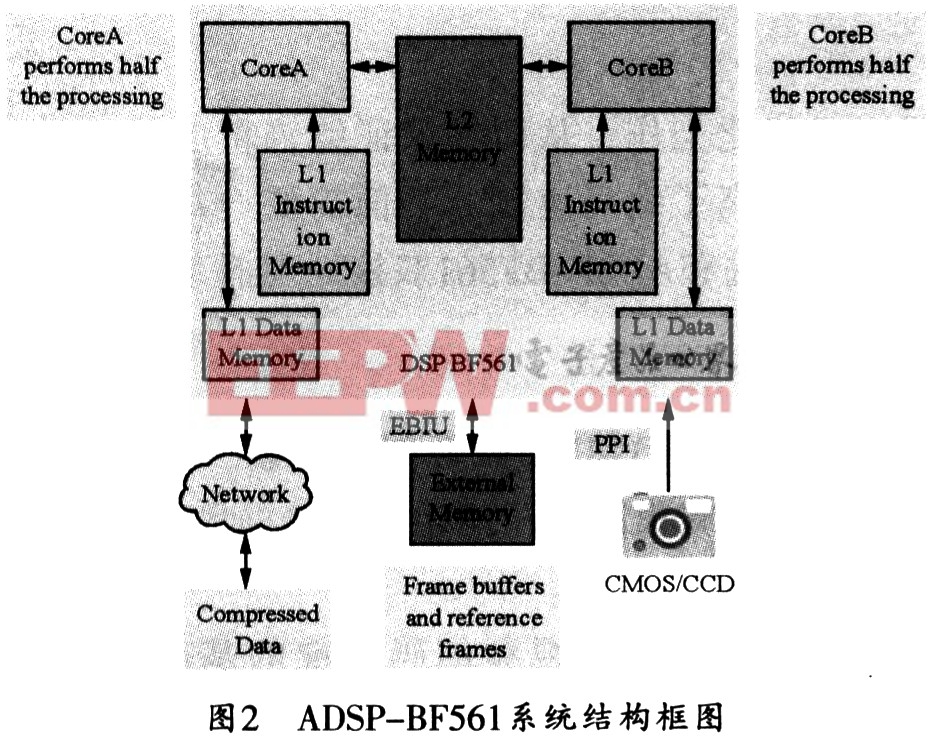

ADSP-BF561是一種雙核750 MHz處理器,具有對稱多處理(SMP)系統結構。其SMP結構在信號處理和控制功能的集成和分割方面能夠為用戶提供較高的性能和較大的設計靈活性。ADSP-BF561的系統結構如圖2所示,它包含coreA和coreB兩個核,每個核的處理頻率可達750MHz。兩個核都有各自獨立的32KB L1指令存儲器(16KB Cache/SRAM)和64KB L1數據存儲器(32KB Cache/SDRAM),并可共享128KB L2存儲器。兩內核訪問不同內存時,其速率有明顯差異,其中訪問L1存儲器最快,L2次之,而訪問片外內存和設備則最慢。

由于訪問存儲器速率的差異。雙核之間進行數據交換最好在L1段直接進行,而且需要使用IMDMA控制器。這個DMA控制器的主要功能是在雙核之間的L1存儲器之間進行數據交換。使用IMDMA控制器可以在訪問速率比較慢的片外內存或者對L2進行數據處理操作時,提高數據處理的速率,進而提高編碼效率。

2 H.264視頻編碼算法的優化與實現

對編碼器的優化主要是對P幀編碼流程的優化和對ADSP-BF561雙核處理系統的優化,合理的流程有利于各種模塊的獨立性和完整性,同時有利于以后只針對某個模塊的優化或升級處理。而利用ADSP-BF561的雙核協調處理優勢可以進一步提高其速度。

評論