基于FPGA+MCU的大型LED顯示屏系統設計

傳統的大型LED顯示屏系統以單片機MCU、ARM 或PLD為核心控制芯片,以FPGA為核心的led顯示屏控制系統設計實現起來比較復雜,并且需要以高性能的FPGA芯片作為基礎,而以微處理器為核心的LED顯示屏控制系統不夠靈活,在改變LED屏幕顯示尺寸時,需要大幅修改系統設計,PLD雖在處理速度上有較大提高且能很好地控制多模塊顯示,但其在時序電路描述方面明顯不如FPGA。提出了基于FPGA與單片機MCU的大型LED顯示屏系統設計方案,該系統中FPGA為主控制單元,單片機為掃描控制單元,該方案簡化電路,提高系統的靈活性和可靠性。實踐仿真結果表明:系統顯示內容較多,能較好地支持彩色顯示,降低了功耗,實現了現場實時控制顯示。

本文引用地址:http://cqxgywz.com/article/168397.htm隨著平板顯示技術的不斷更新,大型LED顯示系統利用發光二極管構成的點陣模塊或像素單元組成大面積顯示屏,主要顯示字符、圖像等信息,具有低功耗、低成本、高亮度、長壽命、寬視角等優點。近年來廣泛應用在證券交易所、車站機場、體育場館、道路交通、廣告媒體等場所。

通常用單一單片機作為主控器件控制和協調大屏幕顯示。由多片單片機構成的多處理器系統,其中一片作為主CPU,其他作為子CPU共同控制大屏幕的顯示,該系統可以減輕主CPU 的負擔,提高了LED點陣的刷新頻率。但單片機的驅動頻率有限,無法驅動等分辨率LED屏幕,尤其是對于多灰度級彩色大屏幕,數據送到顯示屏之前要進行灰度調制重現圖像的色彩,對數據的處理速度要求更高,單片機控制在速度上無法滿足上述要求。因此該方案主要應用于實時性要求不高的場合,主要進行一些文字、圖片等靜態異步顯示的控制。視頻圖像信號頻率高、數據量大,要求實時處理,采用FPGA/CPLD設計控制電路,其中的同步控制、主從控制、讀寫控制和灰度調制等大量電路進行了集成,簡化系統結構,便于調試且系統結構緊湊,工作可靠。與單片機控制電路相比,電路結構明顯簡潔,電路的面積減小,可靠性增強,調試也更為簡單,由于FPGA/CPLD可以并行處理多個進程,比起單片機對任務的順序處理效率更高,點陣的刷新頻率也隨之提高。

對實時性要求較高、數據量較大的場合下,可編程邏輯器件是首選的核心數據處理器。本系統考慮對于傳輸視頻數據大小和驅動LED大屏幕刷新頻率的要求,LED發送卡、接收卡均采用FPGA作為核心處理器,筆者選擇Xilinx公司基于90nm工藝制造的XC3S250E-FTG256,內有25萬邏輯門,最高頻率可以達到600MHz,完全可以滿足系統速度的要求在系統中作為掃描控制單元,同時以MCU芯片為主控制單元。采用該方案可以有效簡化顯示屏的電路結構,從而提高了整個控制系統的靈活性和可靠性。

1 系統的組成和工作原理

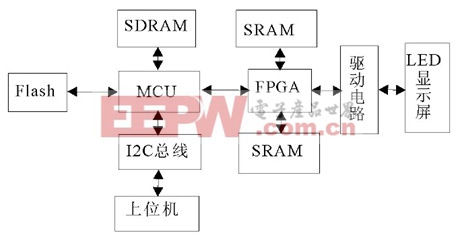

該系統采用89C51單片機和SDRAM 組成控制中心,由基于Xilinx公司的FPGA的90nm工藝制造的XC3S250E-FTG256和RAM 組成掃描控制模塊,以FLASH作為存儲器模塊,采用以太網傳輸數據,組成LED屏的控制系統。系統結構如圖1所示。其工作原理為:主機通過TFTP協議將圖片傳輸給系統以太網接口模塊,以太網接口模塊解析協議,接收圖片數據,然后將數據傳輸給MCU,MCU 將接收到的數據寫入存儲模塊NAND FLASH.在顯示時,MCU讀取FLASH 中的數據,通過SPI接口將數據傳輸給FPGA掃描控制模塊,經掃描控制模塊處理后傳輸到LED屏幕上顯示。

圖1 基于FPGA和MCU的LED顯示屏控制系統框圖

2 硬件系統設計

2.1存儲器電路設計

本系統中需要用2片RAM 芯片作為緩存來存儲視頻數據,并以乒乓方式進行快速讀寫操作。目前主要有動態存儲器(DRAM)和靜態存儲器(SRAM),SRAM 的讀寫時間短,靜態功耗比較低,總線利用率高,它不需要刷新電路就能保存內部存儲的數據,但是它的集成度較低,相同的容量占用體積大,價格較高,主要用于性能要求較高的領域。

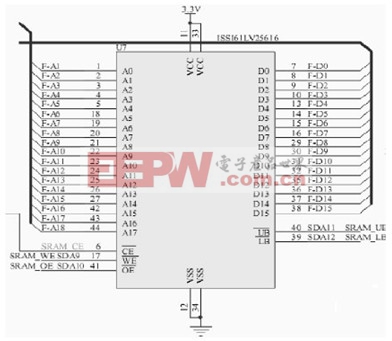

DRAM 只能將數據保持很短的時間,它使用電容存儲,必須經常刷新電路來保存數據,它的讀寫過程比較復雜,時間較長,動態功耗較大,總線利用率比較低。不過DRAM 的存儲容量大,價格便宜,被大量用在服務器和電腦中。由于DRAM 讀寫過程比較復雜,本系統要求存儲器有快速的讀寫響應,所以設計中選用SRAM 作為存儲器。本系統所用的LED屏大小為512×64,每個像素數據(RGB)占用24bit,則一場畫面的數據量為512×64×24=768kbits.本設計選用ISSI公司的IS61LV25616芯片來存儲視頻數據。SAA7111輸出16bit視頻信號,16位數據線正好方便存儲數據。它的容量為256×1 024×16bit,足夠存儲一場視頻數據,并有留有充足的容量供系統以后的升級。SRAM 的電路設計如圖2所示。

圖2 SRAM 電路

評論