用FPGA實現DSP與液晶顯示器的快速接口

隨著器件集成工藝的發展和Soc器件的出現,現在的數字系統正在越來越多地采用可編程器件設計。這樣,不僅開發周期短,而且在價格和使用難易度上也顯示了很大的優勢。更為重要的是,還能利用器件的現場可編程特性,根據應用的要求對器件進行動態配置,簡便易行地完成功能的添加或變化。

本文引用地址:http://cqxgywz.com/article/169432.htm在高速的數字信號處理系統中,要涉及到大量的計算,為了提高運算速度,正大量使用DSP器件。目前的可編程器件,其時鐘頻率可以很高,在高速數字信號處理系統中將發揮越來越大的作用。因此,DSP+FPGA的方案正越來越多地被電子工程師們采用。

在很多的實際數字系統中,往往需要良好的用戶界面,其中LCD是被大量采用的顯示器件。由于LCD是典型的慢速設備(相對于DSP來講),在與高速微處理器接口時,會耗費大量時間,這在高速系統設計中是不允許的。如果DSP有不太富裕的處理余量,如何利用它對LCD完成控制呢?僅僅在兩者之間加入鎖存器之類的簡單接口電路,往往不能對LCD完成控制。不過,有了FPGA,就可以在不增加成本的情況下,在DSP和LCD之間設計一條雙向的快速通道。

1 DSP和LCD的時序

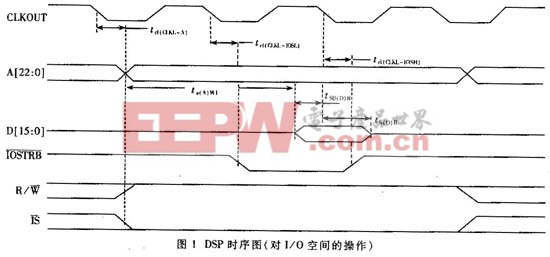

TI公司是DSP在全球的主要供應商,其低價位的TMS320VC54x系列DSP深受廣大電子工程師的青睞。下面以TMS320VC5416為例介紹DSP的時序。TMS320VC5416將尋址范圍分為存儲器空間、程序空間和I/O空間。其中,對I/O空間的操作由地址線、數據線和三根信號線IOSTRB、R/W和IS來完成,其時序圖如圖1所示。

讀操作和寫操作由R/W信號線上的高低電平決定。如果不采用外部插入等待周期的方法,僅靠內部的等待周期設置寄存器,訪問外部I/O空間時最多可以插入14個等待周期。如果DSP運行在100MHz的主頻上(實際上TMS320VC16可以運行在最高160MHz的主頻上),也只有0.14μs。這對于LCD來說來遠遠不夠的。

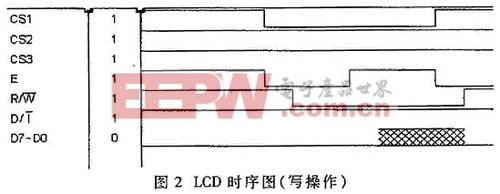

常見的192×64點陣的LCD(FM19264)實際上是由3塊獨立的64×64點陣LCD構成的,共享地址線和數據線,可由CS1、CS2和CS3分別選中。每小塊LCD都有各自獨立的指令寄存器和數據寄存器,由控制線D/I上的高低電平選擇。數據的鎖存或出現在數據線上由E信號決定。LCD主要控制管腳的功能如表1所示。對LCD寫操作的時序圖如圖2所示。LCD的每次讀寫操作最少要1μs。如果能使DSP對LCD的訪問象對高速設備訪問一樣,就能夠最大限度地減小DSP資源的浪費,并且能夠減少系統的復雜性,這就需要在FPGA中添加一個DSP與LCD之間的高速雙向通道。

評論