改進的解耦雙同步坐標系鎖相環的設計與實現

摘要:微網中的電壓可能會存在較大的諧波和不平衡,因此要求鎖相環(PLL)能夠迅速、準確地確定電網正序電壓的相位。提出的改進型解耦雙同步坐標系PLL通過在q軸加入6次諧波的陷波器,可抑制電網中的5次負序電壓和7次正序電壓對鎖相的影響。鎖相程序在相位變化較大時改變正弦表的指針,在相位或頻率變化較小時調節DSP周期寄存器。實驗證明了該鎖相方法的有效性。

關鍵詞:鎖相環;雙同步坐標系;解耦陷波器

1 引言

在微網中,由于電壓可能會存在較大的不平衡和低頻諧波電壓,因此對于并網逆變器而言,能夠準確地獲取電網的基波正序電壓就尤為重要。文獻對常規的d—q變換進行了分析。該變換在電網電壓完全對稱且沒有諧波的情況下能夠準確地獲取電網電壓的相位。當電壓存在不平衡或諧波時,鎖相得到的相位就會存在誤差和波動。降低系統帶寬可抑制高頻諧波,但減慢了PLL的響應速度,反之亦然。

文獻提出在鎖相回路中加入巴特沃斯低通濾波器的方法,通過低通濾波器來抑制鎖相回路中的低頻諧波分量,其仿真和實驗證明該方法能顯著提高在電網不平衡和存在諧波時的鎖相精度。文獻先對各相電壓進行鎖相,然后再采用正負序分離的方法,獲得電網電壓中的正序分量,最后再采用常規的d—q鎖相。該鎖相方法能夠消除電網電壓不平衡造成的影響,并且對諧波電壓具有較好的抑制能力。文獻提出采用解耦雙同步坐標系的方法同時對電網中的正負序電壓進行提取,然后將正負序電壓進行解耦,可以很好地抑制電網中的負序電壓。

在上述基礎上,在此提出通過在正序q軸鎖相回路中加入300 Hz陷波器的方法抑制電網電壓中存在的5次負序電壓和7次正序電壓對鎖相的影響。鎖相程序針對較大的相位變化采取改變正弦表指針的方法,針對較小的相位或頻率變化采取調節DSP周期寄存器的方法。該實現方法能更好地兼顧鎖相的動態性和精確性。

2 改進的解耦雙同步坐標系PLL

2.1 解耦雙同步坐標系模型

電網電壓的表達式為:

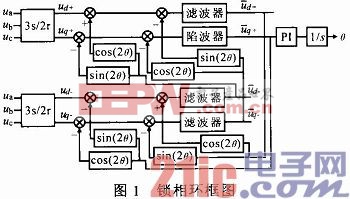

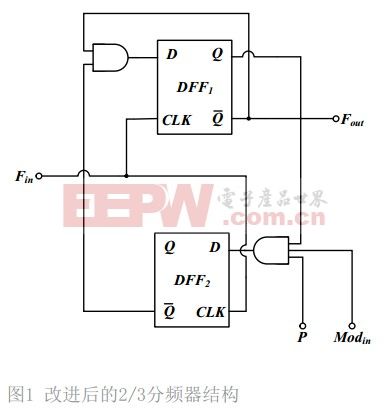

式(4)反映了正負序電壓之間的耦合關系:負序d,q分量以一個2倍頻分量耦合到正序分量中;正序d,q分量也以一個2倍頻分量禍合到負序中。通過式(4)可解耦得到正負序電壓中的直流分量,從而抑制電網不平衡對鎖相造成的影響。改進的基于解耦雙同步坐標系PLL的框圖見圖1。

dc相關文章:dc是什么

低通濾波器相關文章:低通濾波器原理

鎖相環相關文章:鎖相環原理 鎖相放大器相關文章:鎖相放大器原理

評論