數字信號在不同時鐘域間同步電路的設計

摘要:文中從控制信號和數據通路兩個方面入手,設計了信號在不同時鐘域之間的同步電路。采用直接鎖存法和鎖存反饋法來控制信號的跨時鐘域傳遞,電路簡潔、高效;采用異步FIFO (First In First Out)實現數據信號的同步,并通過格雷碼和兩級鎖存來進行指針的跨時鐘域傳遞,FIFO緩沖區的空滿判斷采用修改后的格雷碼,對n+1位的編碼可以節省(n2-n-2)/2次異或操作。該設計解決了信號跨時鐘域傳遞時可能出現的亞穩態問題。

關鍵詞:同步電路;異步FIFO;格雷碼;亞穩態

隨著系統應用需求的不斷增多和集成電路技術的快速發展,大規模數字電路中常包含多個時鐘域,設計中不可避免地要完成數字信號在不同時鐘域間的傳遞,這時,如何保持系統的穩定,順利完成控制信號和數據通路的傳輸就變得至關重要,這也是電路設計中最為棘手的問題之一。如果不采取一定的措施,控制信號和數據通路的接收方極易產生亞穩態信號,從而造成電路的同步出錯。本文討論了控制信號和數據通路的同步,提出了解決方案。

1 控制信號的同步技術

控制信號的同步分從快時鐘域到慢時鐘域、從慢時鐘域到快時鐘域的轉換和異步輸入控制信號的同步三種情況。分別采用直接鎖存法和鎖存反饋法來實現。

1.1 直接鎖存法

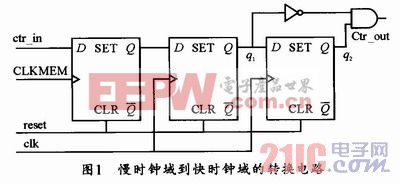

控制信號從慢時鐘域到快時鐘域轉換時,由于控制信號的有效寬度為慢時鐘域周期,需要做特殊處理,保證跨時鐘域后有效寬度為一個快時鐘周期,否則信號轉換到快時鐘域后可能被誤解釋為連續的多個控制信號。同步電路如圖1所示,在快時鐘域對控制信號進行兩級鎖存,由于第二和第三個觸發器的輸出延遲一個快時鐘周期,將它們做一個邏輯運算,就可以得到有效一個快時鐘周期的控制信號。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論