高電源抑制的基準源的設計方案

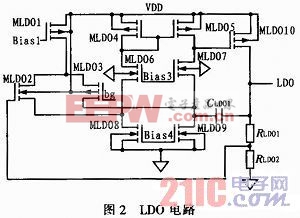

1.2 LDO

LDO在低頻時的PSR主要取決于運放的增益,為此選擇折疊共源共柵電路。此LDO電路基于文獻中的電路修改,如圖2所示,并采用PSR高的偏置生成電路。

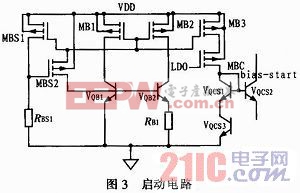

1. 3 啟動電路

Brokaw核心本身存在0狀態,VQC5基極為高電平,VQC2、VQC1基極為低電平,因此引入如圖3的啟動電路。

圖3中右下角即為啟動電路。對于常規Brokaw基準,當VQC2基極電壓低于啟動電壓時,VQCS2將VQC5基極電壓拉低VQC2基極電壓拉高,使電路啟動,所以VQCS2僅需很小的基極電流就可以使電路啟動。

電子鎮流器相關文章:電子鎮流器工作原理

評論