高速PCB中電源完整性的設計

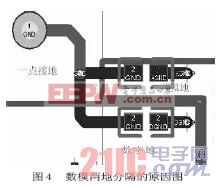

如在圖4中所示,在數字器件和模擬器件共存的高速PCB中,為了防止數字器件所帶來的高頻噪聲對模擬器件造成影響,我們把數字地和模擬地進行了分隔,分立的數字地和模擬地用0歐電阻通過一點接地最后與電源地相連形成回路。這樣就把數模兩部分噪聲進行了隔離,但同時也引進了問題,由于地層的分隔破壞了地層的連續性,阻礙了信號的小環路回路,這就使信號回路阻抗增大,增加了出現電源完整性問題的可能,同時大回路的返回路徑也增大了回路的射頻輻射和板間的電磁兼容性。為了避免以上的問題,在數字器件和模擬器件混合布局中我們提倡采用統一地,就是將數字器件和模擬器件分區布局,而地則不進行分隔。合理地對數模器件進行布局,通過基爾霍夫定律我們知,高頻下電路地返回路徑將沿著最小阻抗,即最小的環路面積返回,數字器件和模擬器件的返回路徑也將分別在數字器件和模擬器件所對應的鏡像路徑返回,它們之間不會引起干擾。

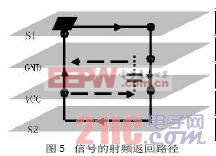

對于高集成度的PCB設計中,由于信號線的走線可能比較復雜,形成的回路面積可能比較大。如圖5,在四層板中,某信號源的信線在頂層經過地層和電源層后從地層傳輸,最后返回。在這個傳輸路徑中,高頻信號線所形成的信號回路非常大。為了解決這個問題,我們在靠近信號線的附近,在電源層和地層之間加了一個電容。這樣,對于高頻信號來說,頂層的信號線在地層上將會產生一個鏡像回路,而地層的信號線將在電源層上產生一條鏡像回路,這兩條鏡像回路將與電源層和地層之間的電容構成回路,這樣我們就盡可能地利用電源層和地層作為回路,減少了返回環路面積,從而減少了產生電源完整性及板間電磁兼容問題地可能性。

五、結束語

現今高速數字電路的設計趨向于復雜,多電源的應用、電源電平的降低、芯片的高反應速度和高敏感度以及PCB的高集成度所帶來的設計影響,板內的電源完整性問題也越來越嚴重且受到廣泛的重視。因此本文通過對電源完整性問題的分析提出了其產生因素,并就電源完整性提出了一些設計方法,這對于優化PCB的EMC設計具有一定的價值。

評論