TIP41C低頻大功率平面晶體管芯片設計

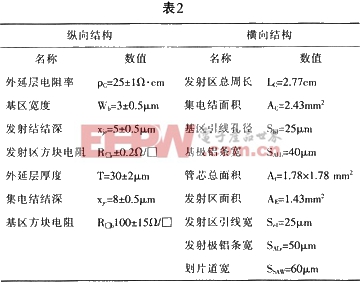

TIP41C的縱向和橫向結構參數如表2所列。該芯片的工藝流程如下:

N型外延片→一次氧化→一次光刻→干氧氧化→B離子注入→深基區擴散→二次光刻→磷預淀積→發射區擴散→特性光刻→特性hFE測試→P吸雜(PSG) →PLTO(低溫氧化)→H2處理→三次光刻→QC檢測(hFE、BVCBO、BVCEO)→蒸鋁→四次光刻→鋁合金→QC檢測VBESAT→五次光刻 →PI膠鈍化→中測抽檢電參數→背面減薄(220μm)→蒸銀→中測測試電參數→入庫

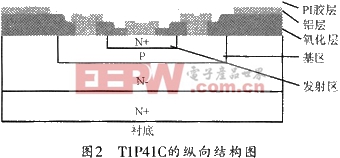

圖2所示是TIP41C的縱向結構圖。

由于作者所在單位的生產車間設計比較簡單,車間環境凈化程度不高,因此,在一次氧化、基區擴散工藝中采用TCA工藝來對一次氧化、二次氧化過程中Na +的污染進行有效控制,發射區擴散采用P-吸雜工藝來控制三次氧化過程中Na+的產生,表面鈍化則采用PI膠工藝來保證外界環境不影響芯片表面,同時進一步吸收、穩定氧化層正電中心的移動,從而使芯片ICEO漏電大大減少,目前,TIP41C的電參數達到國際先進水平。

4 結束語

大量生產數據表明,我司設計的TIP41C晶體管芯片生產成本低,芯片尺寸1.78×1.78 mm2(為目前市場最小),生產原材料完全采用國產材料,目前,該芯片的關鍵電參數(大電流特性和飽和壓降)已達到國際先進水平,因而具有極強的市場競爭力。

評論