采用靜態(tài)CMOS和單相能量回收電路的乘法器電路設計

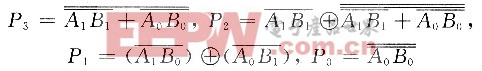

為了能用基本的與非門、或非門和異或門電路實現(xiàn)乘法器,上式可以通過邏輯運算變換為:

本文引用地址:http://cqxgywz.com/article/186047.htm

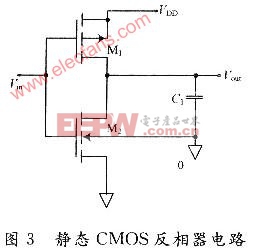

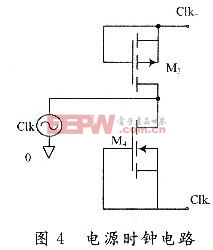

實現(xiàn)電路時,將靜態(tài)CMOS電路(見圖3)構(gòu)成的與非門、或非門和異或門的電源用圖4所示的電源時鐘電路代替即可。其中Clk+,Clk-分別接CMOS電路中PMOS和NMOS管的D極和S極。

2.2 仿真結(jié)果

在PSpice環(huán)境下,分別仿真了用靜態(tài)CMOS電路和單相能量回收電路構(gòu)成的兩位乘法器電路(見圖5和圖6),圖中只顯示了輸出4位積的低2位P1P0,其中輸入信號A1A0,B1B0波形見圖6。其他參數(shù)如下:采用CMOS 1.2μm技術(shù),正弦波峰峰值為2.5 V,直流電壓VDD為2.5 V,并假設乘法器的輸出端接負載電容為O.1 fF。

p2p機相關(guān)文章:p2p原理

評論