基于AD7543和FPGA的數/模轉換電路設計

數/模轉換(D/A)電路,是數字系統中常用的電路之一,其主要作用是把數字信號轉換成模擬信號,通常是利用專用的數/模轉換(D/A)芯片來實現的。AD7543是Analog Device公司生產的的12位數/模轉換(D/A)芯片,它采用串行數據輸入形式,即數字信號被一位一位地寫入AD7543數/模轉換(D/A)芯片中,因此,AD7543要與一個控制器配合使用才能發揮作用。常規的方法,是以CPU作為控制部件,通過軟件編程的方式來控制AD7543,從而實現數/模轉換功能的。軟件實現法雖然簡單,但必將會占用大量的CPU時間,削弱了CPU實時處理能力,降低了系統的可靠性。針對以上情況,在此設計了基于可編程邏輯器件(FPGA)數/模轉換電路,利用可編程邏輯器件(FP-GA)直接控制模轉換(D/A)芯片AD7543進行數/模(D/A)轉換,取代傳統的“CPU+專用的數/模轉換(D/A)芯片”設計結構,有利于提高系統的抗干擾能力和可靠性。

1 AD7543簡介

1.1 AD7543主要特性

AD7543主要特性為:

分辨率:12位;

非線性誤差:±1/2 LSB;

輸入方式:串行正或負選通;

初始化:異步輸入清零方式;

工作電壓:+5 V;

最大功耗:40 mW。

1.2 封裝形式和引腳功能

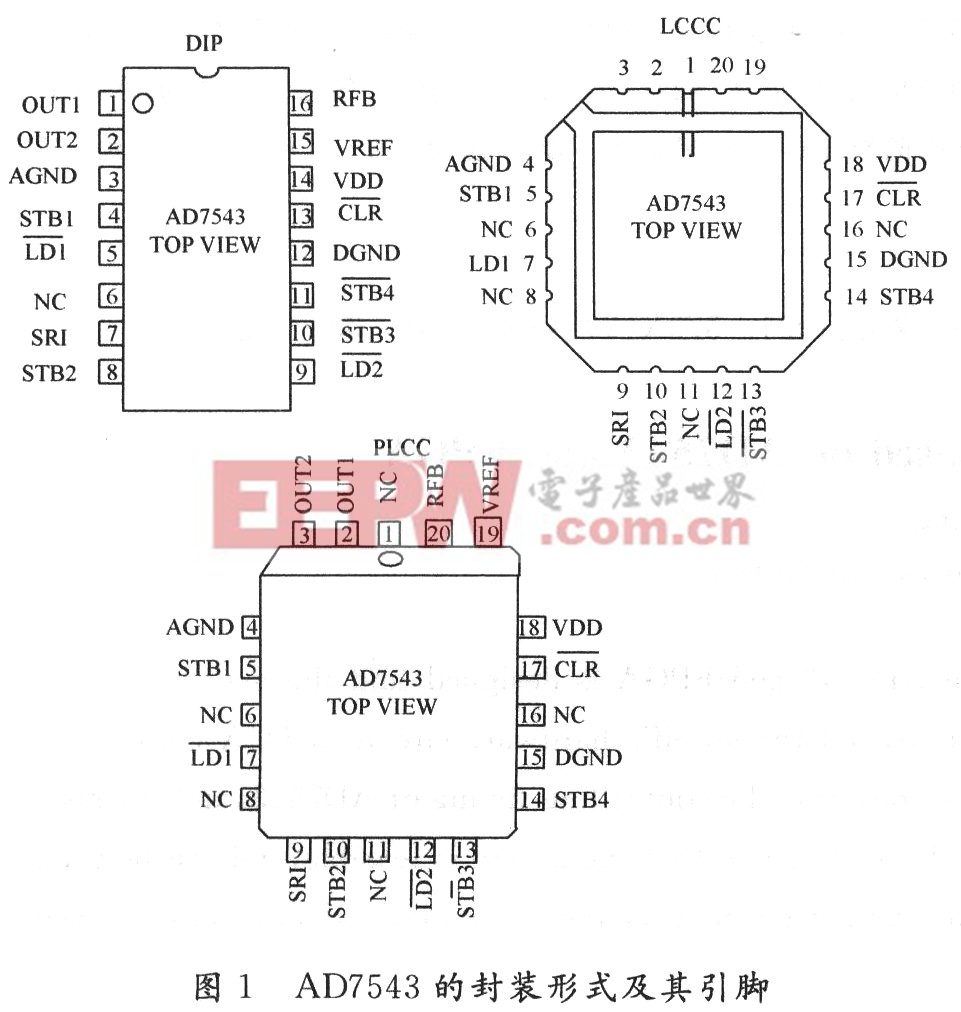

AD7543有三種封裝形式:16引腳的DIP和20引腳的PCCC與PLCC,其封裝形式如圖1所示,設計者可根據實現需求進行選擇,其引腳功能說明如下:

OUT1:數/模轉換(D/A)器電流輸出端,通常接到放大器正輸入端;

OUT2:數/模轉換(D/A)器電流輸出端,通常接到模擬地;

AGND:模擬地端,接到模擬地;

STB1:寄存器A選通1信號輸入端;

LD1:寄存器B裝人選通1輸入端,LD1和LD2都為低電平時,寄存器A的內容被裝入到寄存器B中;

N/C:懸空;

SRI:串行數據輸入端,與寄存器A低位相連;

STB2:寄存器A選通2信號輸入端;

LD2:寄存器B裝入選通2輸入端,LD1和LD2都為低電平時,寄存器A的內容被裝入到寄存器B中;

STB3:寄存器A選通3信號輸入端;

STB4:寄存器A選通4信號輸入端;

DGND:數字地端;

CLR:異步清寄存器B輸入端,當為低電平時,清寄存器B內容,寄存器A內容不變;

VDD:5 V供電輸入端;

VREF:參考電壓輸入端;

RBF:反饋輸入端。

評論