利用Cadence設計COMS低噪聲放大器

在版圖編輯器(Layout XL Edit)的Verify菜單當中,可以找到DRC,LVS,Extract對應的選項;在完成了必要的參數設置之后,便可以完成電路的物理驗證。在做完寄生參數提取之后,便可以利用包含寄生參數的電路完成電路后仿真(Post-layout simulation),從而得到與實際電路性能更為接近的各項仿真結果。

(3)實驗結果。在完成最終電路的調試后,得到了各項仿真結果。

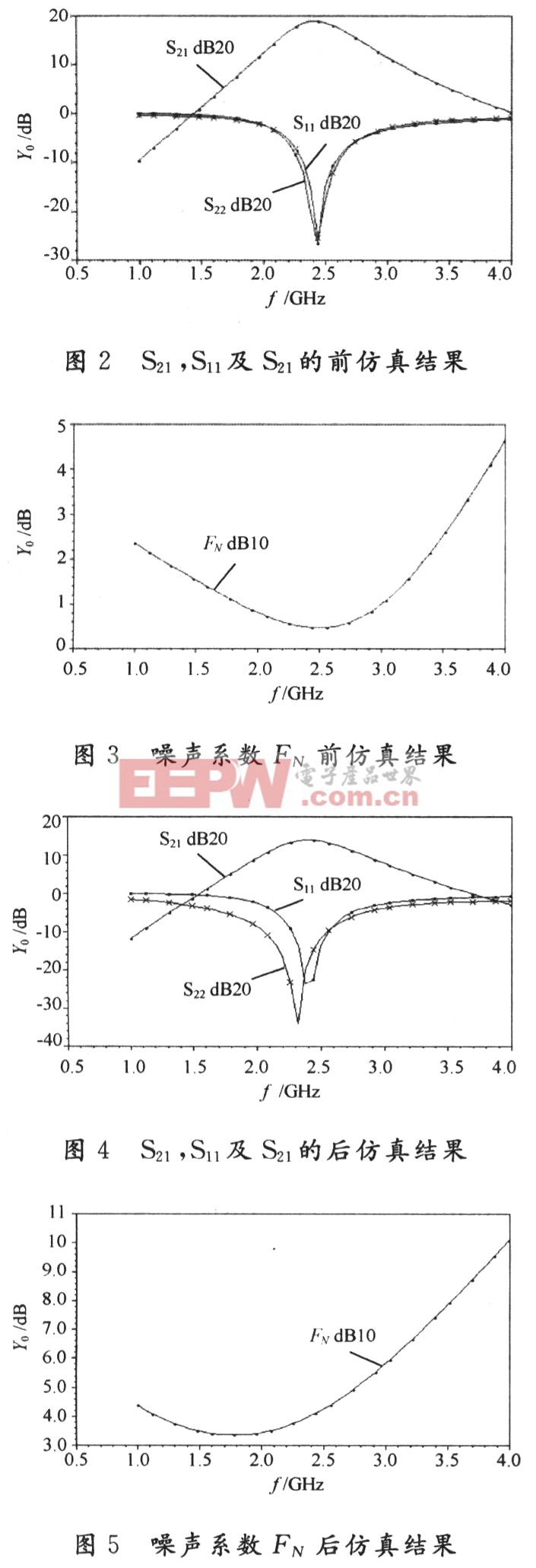

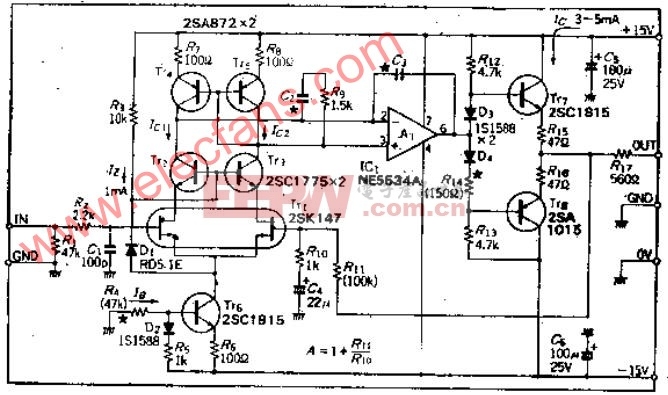

圖2、圖3分別是用電路原理圖仿真(即前仿)得到的S參數以及噪聲系數FN的實驗結果。本文引用地址:http://cqxgywz.com/article/188860.htm

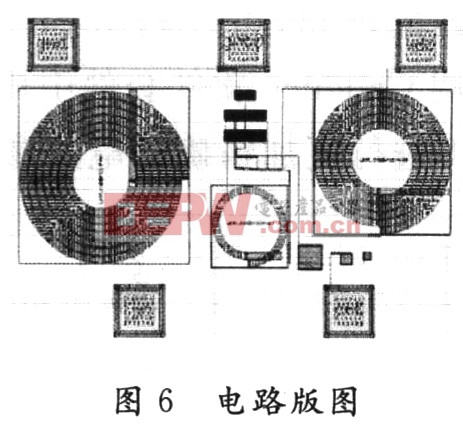

圖4、圖5是完成版圖之后,考慮寄生參數的電路后仿真結果。圖4是S參數的后仿真結果。由S11,S22的曲線可知,在2.4 GHz的中心頻率附近,S11,S22-10 dB。可見,輸入、輸出電路均有比較好的匹配。圖5是噪聲系數FN的后仿真結果。圖6為電路版圖。

與電路的前仿結果相比,后仿真的噪聲系數有一定的上升,這說明電路中的寄生參數會使電路的噪聲性能惡化。

3 結 語

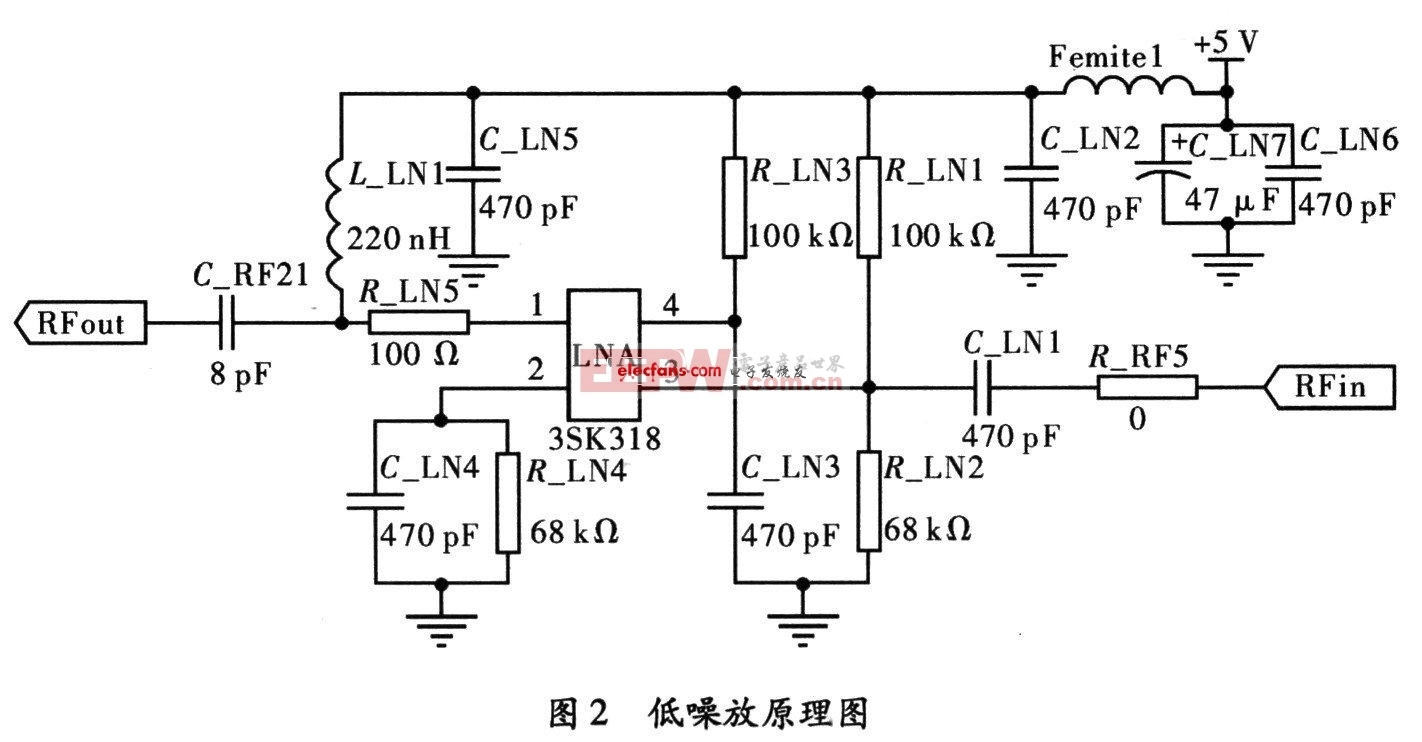

結合一個具體的低噪聲放大器(LNA)設計實例,采用CHRT的0.35μm RFCMOS工藝,在EDA軟件IC 5.1設計環境中設計了一個2.4 GHz的低噪聲放大器。設計過程中完成了電路原理圖仿真、版圖設計以及后仿真。實驗結果表明該低噪聲放大器具有較好的電路性能。結合設計過程,還介紹了如何運用Cadence軟件對CMOS低噪聲放大器進行電路設計和仿真。

西門子plc相關文章:西門子plc視頻教程

評論