SOPC大規(guī)模可編程專用集成電路的快速開發(fā)

引言

本文引用地址:http://cqxgywz.com/article/189692.htm在通常情況下,專用集成電路(ASIC)是大批量高性能應用系統(tǒng)設計師的理想方案。但是,設計ASIC需要昂貴的設計工具,這樣開發(fā)成本很高,當要把產品及時地推向市場時就會承擔很大的風險。據初步統(tǒng)計,超過60%的ASIC設計至少要進行一次以上的重制,導致產品面市推遲、成本預算超支。

HardCopy II體系結構建立在被稱為Hcell的精細粒度晶體管陣列上。 Hcell支持從Stratix FPGA的無縫移植,具有ASIC技術那樣的密度、成本、性能和功耗優(yōu)勢。使用HardCopy器件,利用原有的FPGA開發(fā)工具,將成功實現于FPGA器件上的SOPC系統(tǒng)通過特定的技術直接向ASIC轉化,從而克服傳統(tǒng)ASIC設計中普遍存在的缺點,如開發(fā)周期長、產品上市慢、一次性成功率低、有最少投片量要求、設計軟件工具繁多且昂貴、開發(fā)流程復雜等,是快速開發(fā)大規(guī)模可編程專用集成電路(ASIC)前景最看好的發(fā)展方向。

Hardcopy II器件和Stratix II FPGA器件引腳完全兼容。在芯片正式投產之前,設備制造商可以使用FPGA進行設備小規(guī)模生產,采用Stratix FPGA對設計進行測試,然后,設計中心將設計無縫移植為低成本、功能等價、引腳兼容的HardCopy II ASIC器件。

1 基于SOPC技術的Stratix FPGA的開發(fā)

采用Stratix FPGA實施高密度邏輯設計,無論設計是在單個器件中進行ASIC原型開發(fā),還是面向批量生產,都能夠很方便地使用Stratix FPGA來實現,一旦需要便可以移植為HardCopy結構化ASIC。

最新推出的Stratix V及HardCopy ASIC采用高性能28 nm工藝制造,是高端密度的領軍者。

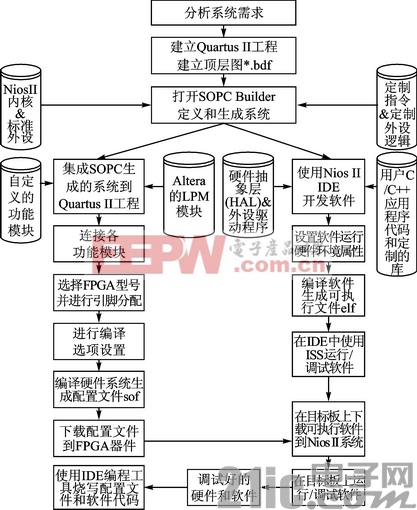

Stratix FPGA的開發(fā)基于Quartus II 軟件進行系統(tǒng)硬件設計,Quartus II 軟件在高密度FPGA設計中能夠實現最佳效能,以最快的速度完成設計。Quartus II 軟件是在統(tǒng)一設計環(huán)境下,一套完整的綜合、優(yōu)化和驗證工具,使用漸進式編譯功能,與傳統(tǒng)的高密度FPGA流程相比,設計迭代時間縮短了近70%,顯著提高了設計的效率。

Quartus II用來建立硬件的系統(tǒng),主要使用SOPC Builder工具。SOPC Builder用來建立SOPC系統(tǒng)模塊,Quartus II支持多種設計方式,如原理圖、硬件描述語言等,硬件描述語言的方式支持VHDL和Verilog。SOPC Builder提供大量基于Avalon總線的IP外,它還是一個開發(fā)的IP集成環(huán)境,用戶可以很容易地將自己設計的IP集成到SOPC Builder中,實現設計重用。若嵌入DSP系統(tǒng),

可使用MATLAB/DSP Builder進行DSP模塊設計,經由MATLAB/DSP Builder設計的DSP模塊或其他功能模塊可以成為單片FPGA電路系統(tǒng)的一個組成部分,實現一定的功能。另一方面,可以通過MATLAB/DSP Builder,為嵌入式處理器設計各類加速器,并可以以指令形式加入到Nios II的指令系統(tǒng),從而成為Nios II 系統(tǒng)的一個接口設備,與整個片內系統(tǒng)融為一體。即利用DSP Builder和Nios II CPU,用戶可以根據項目的具體要求,隨心所欲地構建自己的DSP處理器系統(tǒng)。

SOPC Builder提供3種Nios II 處理器軟核,即經濟型、標準型和快速型內核,供使用者根據設計具體情況來選擇。Nios II嵌入式處理器是一種面向用戶的、可以靈活定制的通用RISC(精簡指令集架構)嵌入式CPU。它是一款具有廣闊應用前景的處理器,融入了許多新的設計方法和理念,其SOPC概念體現在以下兩個方面:

① Nios II符合工業(yè)技術的發(fā)展潮流,即硬件設計軟件化。采用Nios II能有效地降低人力和物力成本,提高產品競爭力;硬件設計軟件化還能方便對硬件進行仿真、驗證,整體系統(tǒng)結構的數字邏輯化設計使得驗證工作可通過仿真軟件順利地實現,可以掌握詳細、清楚的信息;減少了硬件設計的錯誤,使得對硬件接口不是很熟悉的人也可以進行系統(tǒng)平臺的集成。

② Stratix FPGA的軟件開發(fā)使用Altera公司的系列FPGA開發(fā)的集成軟件開發(fā)環(huán)境Nios II EDS。Nios II系統(tǒng)是嵌入式處理器的基本軟件開發(fā)工具。所有軟件開發(fā)任務都可以在Nios II IDE下完成,包括編輯、編譯、程序調試、下載和運行。Nios II IDE具有編碼生成環(huán)境以及可選RTOS和TCP/IP庫集成。它還提供構建管理工具,使用GNU編譯器作為其支撐技術。此外,Nios II IDE還具有片內閃存編程器功能。

Nios II軟核及其開發(fā)平臺(Nios II IDE)幫助開發(fā)者將大部分模塊構建好,卻又不失靈活性,對大多數外設開發(fā)了相應的驅動程序。對于特殊要求的設計,Nios II開發(fā)平臺提供了以下工具:

對時間要求苛刻的軟件算法可以采用用戶定制指令或C2H編譯器進行加速;可以方便的把實時操作系統(tǒng)μC/OSII移植到Nios II處理器;支持用戶定制外設,創(chuàng)建定制的SOPC元件,需要更新時可以使用元件編輯器對整個元件進行再次編輯。

Stratix FPGA總體開發(fā)流程如圖1所示。

圖1 Stratix FPGA總體開發(fā)流程

評論