利用CPLD實現FPGA的快速加載

(4)加載模塊。當檢測到CPU的標志時CPLD開始發送數據對FPGA進行加載,加載完成后對自身的發送完成標志取反,關閉輸出使能。要注意不同芯片廠家的加載高低位順序不同。FPGA是靠dclk的上升沿來采樣數據的,所以在dclk的下降沿將數據從CPLD送出,這樣在FPGA端采樣時dclk的上升沿正好對著數據的中間,能獲得最大的時序窗口,如圖10所示。本文引用地址:http://cqxgywz.com/article/189703.htm

實現程序如圖11所示。

(5)加載結束后,FPGA將conf_done信號拉高,CPLD通知FPGA加載已經完成。

3 功能、性能測試

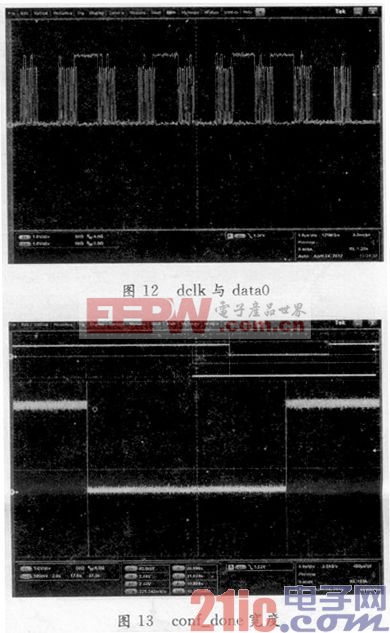

為了驗證方案的有效性,選用Altera的FPGA(EP4SGX530),CPLD(EPM570F256CS),MPC8548搭建了一個加載系統,測試結果如圖12所示,橫軸表示時間,有固定周期的信號為dclk。由圖可知加載成功,加載時鐘頻率約為17 MHz。總體加載時間可由conf_done信號指示,如圖所示橫軸表示時間,從圖上可以看出,加載一個10 MB大小的FPGA配置文件大約需要10 s。

4 結論

CPU直接對FPGA進行加載的傳統方式,加載一個10 MB的FPGA配置文件大概需要100 s,利用CPLD對FPGA進行加載,只需要約10 s(Local Bus的訪問周期約為200 ns,相對于CPLD對FPGA的加載時間可以忽略不計,兩者可以并行進行),加載速度提高了10倍左右。在有兩個甚至多個FPGA需要加載的系統,其優勢更為明顯。該方法對只要有CPU,CPLD和FPGA的系統即可移植,并且可以支持Altera,XILINX和LATTICE三大廠家的邏輯器件。

評論