基于FPGA的一種高速圖形幀存設計

2.2 控制模塊

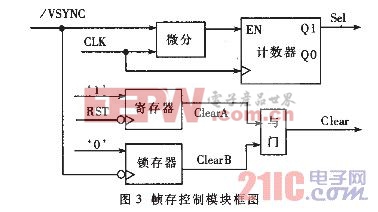

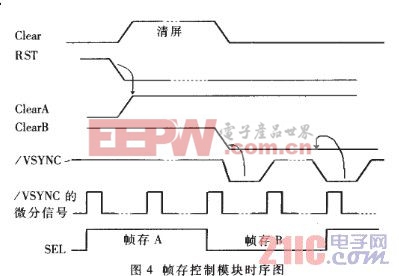

幀存控制器的控制模塊產生體選擇信號Sel和上電清屏時序信號Clear,控制模塊的結構框圖如圖3所示。圖中,/VSYNC是場同步信號,該信號經過一個微分電路,產生一個像素時鐘周期寬的使能脈沖信號,控制計數器的計數使能。計數器為一模2計數器,Sel信號為場同步信號/VSYNC的四分頻,在出現兩個場同步信號之后,才切換幀存,即兩個幀存使用的順序是:AABBAA...這種控制方式類似于電影遮光板的設計思想,使一幅畫面在屏幕上重復出現兩次,從而在25Hz的幀頻時能獲得50Hz的場頻,使系統視頻帶寬增加一倍。如當場頻50Hz時,圖形處理器可以有40ms的時間處理一幀圖形數據。圖4為幀存控制時序圖,Clear信號的產生過程如下:系統上電時,RST信號高一段時間(系統邏輯復位)后變低,在RST的下降沿,ClearA變高,此時場同步低電平有效信號還沒到,ClearB為高,Clear為高,系統開始清屏時序。當對兩個幀存的清屏工作結束時,場同步信號/VSYNC有效,該信號將0電平鎖存輸出,ClearB為低,Clear為低,系統開始在Sel控制下工作。從控制模塊框圖中可以看到,Clear信號僅僅在上電復位信號RST結束時(下降沿)才變為高,持續一個場周期之后,Clear信號將一直為低,把控制權交給Sel體切換信號。控制模塊的VHDL代碼及相應的時序仿真圖如圖5所示(Modelsim5.5FSE仿真器仿真)。

評論