基于FPGA實現的計算機與HDTV顯示器測試信號發生器

6)測試圖案產生模塊

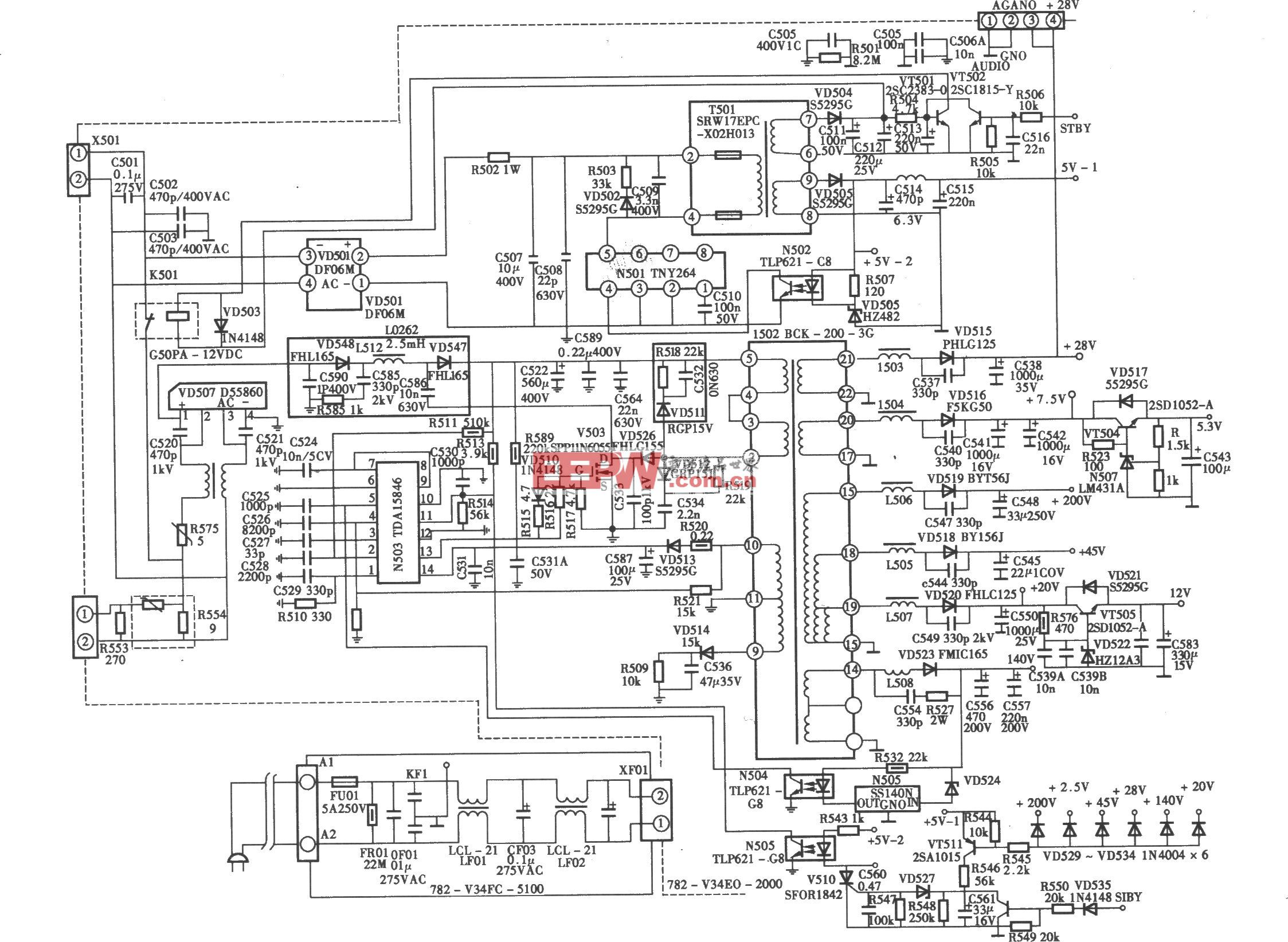

該模塊根據像素計數器和行計數器的計數情況,按照格式選擇信號和測試圖案選擇信號,輸出相應的YCbCr數字電平值.模塊輸出的圖像數據分為黑白數字電平值以及彩色、灰度可變信號電平值.黑白信號的數字電平值比較簡單,只有黑、白、灰3種,且相對固定.而彩色信號包括白、黃、青、綠、品、紅、藍、黑8種電平,灰度可變信號的亮度電平值是在16~235之間變化.在該模塊的設計中,使用了鎖存器,目的是避免測試圖像在電平變化處出現毛刺.圖3是FPGA的程序框圖.表2是改進后系統的部分參數.

圖3 FPGA程序框圖

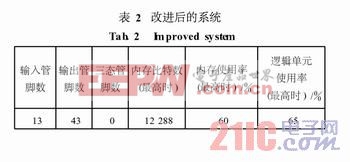

表2 改進后的系統

4 結語

通過采取增加EPROM對FPGA現場配置和設置頻率合成模塊產生十余種像素時鐘及對FPGA的重新編程,使儀器增加了對計算機顯示器進行測試的功能,大大擴展了儀器的應用范圍.本儀器在每種顯示格式下均可輸出13種測試圖案,分別為全白場、全黑場、條形圖、可變窗、五窗口、格形圖、線加窗、PLUGE、2τ脈沖、五階梯、棋盤格、五階梯加可變窗和彩條.

評論