FPGA的輪詢合路的設計和實現

采用這種改進的DRR算法下,可以保證在變長包的情況下,各個接口的整包緩存隊列在報文合路時公平的帶寬,確保合路調度的穩定運行。

DRR整包輪詢合路的基本工作過程為:輪詢4個整包緩存隊列,每讀取一個整包都判斷該包是否是協議包,如果是協議包,則按照上交CPU報文格式送協議FIFO,如果是需要轉發的報文,則按照轉發報文格式送數據報文FIFO。

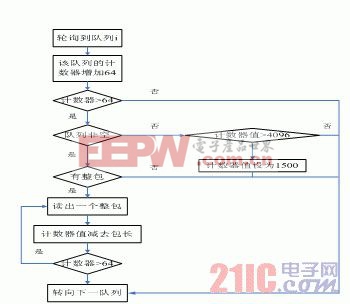

調度機輪詢到某個隊列時,為該隊列的儲蓄計數器加上40;然后判斷該隊列是否為空,如果為空,則馬上轉向下一個隊列;如果非空,則判斷當前該隊列是否有整包,如果當前該隊列無整包,則轉到下一個隊列;否則,如果該隊列目前有整包則輸出該隊列的隊頭包到合路隊列,同時該路的儲蓄計數器的值要減去輸出報文的長度;然后重復上述過程,直到該隊列無整包或者隊列的儲蓄計數器的值小于40時跳轉到下一隊列服務,其詳細工作流程如圖2 所示:

圖2 改進的DRR合路調度流程圖

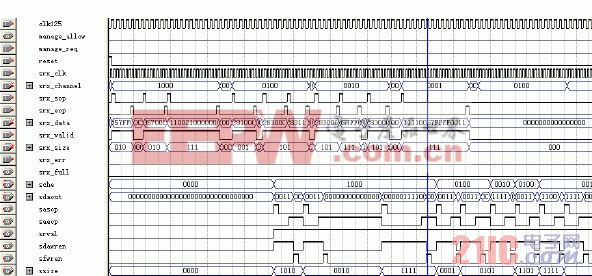

DRR合路調度單元已在ALTERA公司的quartusII4.1環境下用VHDL編程實現,其仿真波形如圖3所示:

圖3 DRR合路調度單元仿真波形圖

仿真結果顯示這種采用分片輪詢和欠賬輪詢的結合的合路調度策略設計可以達到性能需求,確保變長分組合路調度的公平性和穩定性。

3、 結束語

根據SDH芯片的S19202的特點和性能要求,通過在FPGA內部編程實現分片輪詢和改進式欠賬輪詢結合的調度策略,保證了4X2.5G線路接口卡輸入端各個接口合路的公平性和穩定性。經測試該設計性能穩定,整個工作流程簡單實用,符合設計要求。

評論